# 数字 SPWM 方法对系统延时的影响

刘春喜1,孙驰2,高姬1

(1. 辽宁工程技术大学 电气与控制学院,辽宁 葫芦岛 125105;

2. 海军工程大学 舰船综合电力技术国防科技重点实验室,湖北 武汉 430033)

摘要:首先定量分析了对称规则采样和不对称规则采样正弦脉宽调制(SPWM)方法引入的延时,然后介绍了3种改进的SPWM方法:改进的不对称规则采样法、多次采样固定更新法和多次采样立即更新法,并对每种方法引入的延时进行了分析。最后,采用DSP和现场可编程门阵列(FPGA),以同一个正弦信号为参考,同时生成了5种方法的SPWM波形,得到了各个波形基波分量与参考信号的相位差。从相位差可得到各种方法相对于参考信号的延时,与理论分析相一致,证明了所提的3种改进的SPWM方法可以有效地减小延时。关键词:延时:逆变器:SPWM:对称规则采样:不对称规则采样

中图分类号: TM 464

文献标识码: A

DOI: 10.3969/j.issn.1006-6047.2013.06.014

## 0 引言

大功率逆变器的输出电流大,为保证逆变器的可靠性和工作效率,开关频率不宜过高[1-2],采用传统的规则采样正弦脉宽调制(SPWM)方法,会产生较大的延时,给系统的波形质量控制带来不利影响。在中频 400 Hz 系统中,基波频率是 50 Hz 的 8 倍,延时对系统性能的影响更大[3-4]。随着处理器的计算速度越来越快,采样计算时间占开关周期的比例越来越少,这使得控制延时的进一步减小成为可能。

文献[5-7]采用数字控制方法来改进系统的控制性能,但并未考虑数字延时的影响。文献[3-4,8] 考虑了数字延时带来的影响,并通过控制方法来消除延时的影响,不可避免地会增加系统的复杂性。文献[9]详细地分析了数字控制延时对系统性能的影响,但没有提出缩短延时的方法。文献[10-11]分析了一种改进的 SPWM 方法,可以在当前周期更新调制波数据,减小了计算延时,但调制波在1个载波周期内还是更新1次(对称规则采样)或2次(不对称规则采样),因此在低开关频率下由零阶保持引入的延时仍会很大。现场可编程门阵列(FPGA)的出现为PWM 提供了更灵活的实现方法[12-14]。文献[15-16]研究了数字自然采样 SPWM 方法,但没有分析相应的延时。在大功率中频场合下,准确分析 SPWM 过程引入的延时,对系统参数设计有重要意义。

本文定量分析了对称规则采样和不对称规则采样 SPWM 方法引入的延时;为了减小延时,介绍了3种改进的 SPWM 方法,并对它们引入的延时进行了分

基金项目: 国家自然科学基金资助项目(50607020); 辽宁省教育厅科学研究一般项目(L2012109)

Project supported by the National Natural Science Foundation

Project supported by the National Natural Science Foundation of China (50607020) and the Scientific Research Program of Liaoning Education Department (L2012109)

析。最后,通过 DSP 和 FPGA 测量了这 5 种方法引入的延时,实验结果验证了理论分析的正确性。

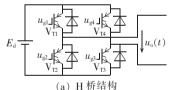

## 1 逆变器主电路及自然采样 SPWM

逆变器主电路采用 H 桥结构,如图 1(a)所示,调制方式为单极性倍频式 SPWM,自然采样波形如图 1(b)所示,载波 c(t)和调制波 m(t)均为标幺值。c(t)由 2个幅值为 1、相位相差  $\pi$  的三角波  $u_{c1}$ 、 $u_{c2}$  组成,设 c(t)周期为  $T_{co}$  m(t)的范围为 -1 ~ 1,分别与 $u_{c1}$ 、 $u_{c2}$  相比较产生 2 对互补的开关信号  $u_{g1}$ 、 $u_{g2}$  和 $u_{g2}$ 、 $u_{g4}$ ,以控制开关管  $V_{T1}$ 、 $V_{T2}$  和  $V_{T3}$ 、 $V_{T4}$ 。

(b) 自然采样 SPWM

图 1 逆变器结构及其自然采样 SPWM Fig.1 Inverter topology and its SPWM with natural sampling

H 桥输出电压为:

$$u_{o}(t) = E_{d}(u_{o1} - u_{o4}) \tag{1}$$

以第 1 个载波周期为例,由相似三角形的几何 关系,可得输出电压  $u_0(t)$ 在该周期内的平均值为:

$$\overline{u}_{o} = E_{d}[m(a) + m(b)]/2 \tag{2}$$

其中,m(a)和 m(b)分别为  $m(t) = u_{cl}(t)$ 时点  $a \setminus b$  的值,如图 1(b)所示。

若载波频率远大于调制波频率,且调制波相对载波变化足够缓慢,则可认为调制波在1个载波周期内保持不变,根据平均值模型分析方法可得 $u_o(t)$ 的基波电压 $u_o(t)$ 为:

$$u_{\rm ol}(t) = E_{\rm d} m(t) \tag{3}$$

自然采样通常采用模拟电路实现,因此在点  $a \ b$  处,从开始采样变量到  $u_o(t)$ 的脉宽发生变化之间的延时为零,所以  $u_{ol}(t)$ 与 m(t)相比不会引入延时。

# 2 规则采样数字 SPWM

采用数字方法实现时,SPWM 常采用对称规则 采样和不对称规则采样。为正确实现数字控制,一般 采用滞后一拍控制,用当前采样周期计算的控制量推 迟1个周期去更新调制波数据,而不是立即更新。

#### 2.1 对称规则采样 SPWM

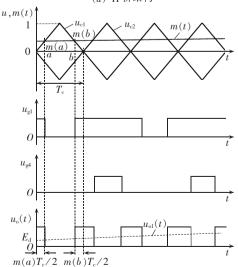

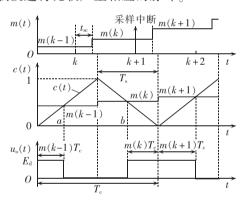

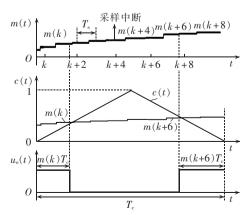

对称规则采样时,采样周期  $T_s = T_c$ ,载波过零时开始采样,并更新调制波数据为上一个采样周期计算所得到的值,如图 2 所示。图中只画出了载波正半波部分,由于计数器时钟频率远大于载波频率,因此可以忽略载波的量化效果。在第 k 个载波周期的起始时刻对 m(t) 采样,控制器按一定的算法对采样值进行计算,经过采样计算时间  $t_{sc}$  后,得到相应的调制波数据 m(k),但调制波并没有直接更新,而是在k+1 时刻更新为 m(k)。所以,调制波数据更新相对于采样时刻滞后了  $T_{co}$

图 2 对称规则采样 SPWM

Fig.2 SPWM with symmetrical sampling

在第 k+1 个载波周期内,调制波数据为 m(k), 其与载波比较,产生相应的脉宽输出,得到合适的  $u_{ol}(t)$ ,该过程称为数字 SPWM 过程。点 a 和 b 采用 的比较值都是在 k+1 时刻更新的值 m(k),相对于 更新时刻的延时分别为  $0.5m(k)T_c$  和[1-0.5m(k)] $T_c$ 。 根据平均值模型分析方法,可得:

$$u_{\text{ol}}(s) = E_{\text{d}}m(s) \left\{ e^{-sm(k)T_{\text{c}}/2} + e^{-s[2-m(k)]T_{\text{c}}/2} \right\} / 2 = E_{\text{d}}m(s)e^{-sT_{\text{c}}/2}\cos\frac{[m(k)-1]\omega T_{\text{c}}}{2}$$

(4)

其中, $s = j\omega$ ,函数  $u_{ol}(s)$ 和 m(s)分别为函数  $u_{ol}(t)$ 和 m(t)的拉氏变换。对于频率远小于载波频率的信号, $\omega T_s \approx 0$ ,则有:

$$u_{\rm ol}(s) \approx E_{\rm d} m(s) e^{-sT_{\rm c}/2} \tag{5}$$

这样数字 SPWM 过程可近似为一个延时环节,延时时间为  $T_{c}/2$ ,等同于零阶保持过程。

所以,采用对称规则采样,从开始采样到输出相应的脉冲宽度,总延时为  $3T_c/2$ ,其中采样计算引入的延时为  $T_c$ ,零阶保持引入的延时为  $T_c/2$ ,用于采样和计算的时间  $t_s$  最大可为  $T_c$ 。

## 2.2 不对称规则采样 SPWM

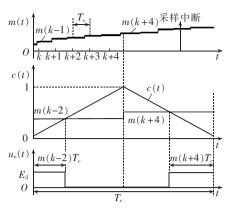

不对称规则采样时,采样周期  $T_s = T_c/2$ ,在载波的过零点和峰值点开始采样,并更新调制波数据为上一个采样周期计算所得到的值,如图 3 所示。每个载波周期采样 2 次,调制波更新 2 次。脉宽数据更新时刻相对于采样时刻滞后  $T_s$ 。

图 3 不对称规则采样 SPWM Fig.3 SPWM with asymmetrical sampling

从 k 到 k+2 时刻间的一个采样周期内,比较时刻点 a 和 b 采用的比较值分别为 k 时刻和 k+1 时刻更新的值 m(k-1) 和 m(k),相对于更新时刻的延时分别为 m(k-1)  $T_s$  和 [1-m(k)]  $T_s$ 。因为采样频率远大于基波频率,连续 2 次采样点间的调制波信号变化很小,所以可近似认为一个采样周期内的 2 个采样值相等。同理,根据平均值模型分析方法,可得:

$$u_{o1}(s) = E_{d}m(s) \left\{ e^{-m(k)T_{s}s} + e^{-[1-m(k)]T_{s}s} \right\} / 2 = E_{d}m(s) e^{-sT_{s}/2} \times \cos\left[ (m(k) - 1/2)\omega T_{s} \right] \approx E_{d}m(s) e^{-sT_{s}/2}$$

(6)

这样数字 SPWM 过程也可近似为一个延时环节,延时时间为 $T_{*}/2$ 。

因为  $T_s = T_c/2$ ,所以采用不对称规则采样,从开始采样到输出相应的脉冲宽度,总延时为  $3T_c/4$ ,其中采样计算引入的延时为  $T_c/2$ ,零阶保持引入的延时为

## $T_c/4$ , $t_s$ 最大可为 $T_c/2$ 。

大功率时开关频率较低,采用规则采样时,采样和计算所需要的时间通常远小于1个采样周期。减小这段时间,由采样计算和采样保持引入的延时均会减小。因此可以通过2个途径来改进SPWM方法:在满足采样计算时间的前提下,让采样点更靠近更新点;在1个载波周期内进行多次采样,计算出新的调制波数据后立即更新。

# 3 改进的 SPWM

下面介绍 3 种改进的 SPWM 法,并对其引入的延时进行分析。

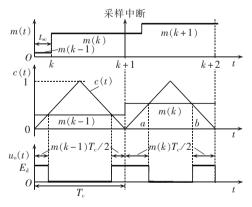

## 3.1 改进的不对称规则采样

为了减小延时,对不对称规则采样进行改进。在满足采样计算时间的前提下,采样时刻不选在载波谷点和顶点处,而是选在更靠近更新点的时刻。若采样计算的最大时间小于  $T_c/N$ ,则采样时刻可选在更新时刻以前  $T_c/N$  处。如图 4 所示,在 k 时刻开始采样计算,得到相应的调制波数据后在下一个顶点处更新调制波数据,该数据在下半个载波周期内保持不变,与载波进行比较产生相应的脉冲。

图 4 改进的不对称规则采样 SPWM

Fig.4 Improved SPWM with symmetrical sampling

采用改进的不对称规则采样,总延时  $t_a$  为  $T_c/N+T_c/4$ , $T_c/N$  为采样计算延时, $T_c/4$  为零阶保持延时。

这种方法的实现需要 3 个定时器,采用 DSP 实现比较困难。可采用 DSP 结合 FPGA 的方法来实现。用 DSP 进行控制计算,用 FPGA 实现 SPWM,在计数到采样时刻时,FPGA 产生一个脉冲,送到 DSP, DSP 接收到该脉冲后开始采样计算,得到相应的调制波数据后送 FPGA,在下一个采样时刻更新调制波数据。当然,只采用 FPGA 也可以实现该方法,只是对控制算法的实现要求较高,且不够灵活。

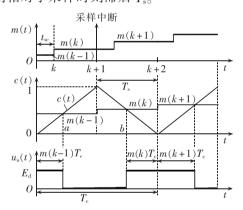

#### 3.2 多次采样固定更新法

多次采样固定更新法的采样计算与载波不同步,如图 5 所示。在一个载波周期内对变量采集 N次,采样后经计算得到相应的调制波数据,并替换上一个值。在载波谷点和峰值点处更新调制波数

图 5 多次采样固定更新 SPWM

Fig.5 SPWM with multiple sampling and fixed updating 据,这样在更新时刻得到的值就是最接近更新时刻所计算出的值。

由于采样计算和载波不同步,调制波更新时刻可能在相应采样周期的调制波数据计算出来之前,如图 5 中第 k-1 个采样周期;可能是之后,如第 k+4 个采样周期。若在计算出来之后去更新调制波数据,则由采样计算引入的延时就小于 1 个采样周期,最小可近似为零;若在计算出来之前去更新调制波数据,由采样计算引入的延时就超过 1 个采样周期,最大可近似为 2 个采样周期。

多次采样固定更新法,总延时  $t_d$  为  $T_c/4~2T_c/N+T_c/4$ ,其中由采样和计算引入的延时在  $0~2T_c/N$  之间,由零阶保持引入的延时为  $T_c/4$ 。N 越大,引入的延时越小,对计算速度要求越高。

#### 3.3 多次采样立即更新

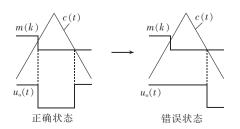

立即更新即计算出调制波数据后立即更新调制 波.通常不采用这种方法的原因有以下 2点。

a. 采用 DSP, 虽然可以实现调制波数据的立即更新,但在 1 个载波周期内,可能会出现错误状态。如图 6 所示,调制波更新前,调制波数据大于载波数据,更新后小于载波数据,因此就不会出现调制波数据和载波数据相等的时刻。这样,本来脉冲在这个时刻应该翻转,由于没有发生比较匹配,脉冲就没有翻转,直到下一次比较匹配时才翻转,这样就会出现脉冲的错误状态。因此采用 DSP 执行数字控制时,通常不采用立即更新方式。

图 6 DSP 执行立即更新时的错误状态 Fig.6 Error status when DSP performs immediate updating

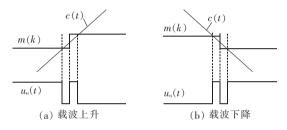

b. 立即更新会产生脉冲竞争现象[11]。如图 7(a) 所示,当调制波数据与载波数据第 1 次相等时,PWM 波由低变高,然后调制波数据变化到另一个值,该值小于载波数据,PWM 波就从高电平变为低电平,直到调制波数据再一次大于载波数据,PWM 波才变为高电平。与自然采样或固定时刻更新相比,输出就多出了 1 个或多个窄脉冲,这就是脉冲竞争现象。在载波下降时同样会出现这种情况,如图 7(b)所示。脉冲竞争现象会增加额外的电平变化次数,增加开关损耗,引入额外的谐波含量。消除竞争脉冲的一个办法是在数字比较器的输出和实际 SPWM 输出之间设置一个窄脉冲消除环节,凡是宽度小于最大竞争脉冲宽度的脉冲都被消除掉。

图 7 脉冲竞争现象 Fig.7 Pulse competition phenomenon

当用 FPGA 实现比较功能时,比较输出可随比较值的变化随时进行翻转,不会出现 DSP 执行时的错误状态。而且,采用 FPGA 也可以比较容易地消除竞争脉冲。因此采用 FPGA,可在 1 个载波周期内执行多次采样,并对调制波数据进行立即更新,文献[15-16]称之为数字自然采样法。

该方法类似于多次采样固定更新法,只是计算得到调制波数据后,立即更新调制波数据。如图 8 所示,在 1 个载波周期内对调制信号进行 N 次采样,采样周期  $T_s=T_c/N$ 。每次采样得到调制波数据后立即更新,用于和载波比较。若在下一次采样的起始时刻正好更新调制波数据,则该方法引入的延时时间等于  $3T_s/2$ ,其中包括采样计算延时  $T_s$  和零阶保持延时  $T_s/2$ 。由于采样计算所用的时间并不是一个固定值,

图 8 数字自然采样 SPWM Fig.8 Digital SPWM with natural sampling

但小于等于  $T_s$ , 所以该方法的延时时间  $t_d \le 3T_c/(2N)$ 。 N 越大, 延时越小, 对计算速度要求越高。

# 4 数字 SPWM 方法比较

当载波周期  $T_c$  一定时,对称规则采样(采样方法 1)、不对称规则采样(采样方法 2)、改进不对称规则采样(采样方法 3)、多次采样固定更新(采样方法 4)以及多次采样立即更新(采样方法 5) 5 种方法的采样周期  $T_s$ 、用于采样计算的最大时间  $t_s$ cmax、引入的延时时间  $t_d$  如表 1 所示。

表 1 5 种 SPWM 方法参数比较 Tab.1 Comparison of parameters among five SPWM methods

| 采样方法 | $T_{ m s}$    | $t_{ m scmax}$ | $t_{ m d}$                                 |  |

|------|---------------|----------------|--------------------------------------------|--|

| 1    | $T_{ m c}$    | $T_{\rm c}$    | $3T_{\rm c}/2$                             |  |

| 2    | $T_{\rm c}/2$ | $T_{\rm c}/2$  | $3T_{\rm c}/4$                             |  |

| 3    | $T_{\rm c}/2$ | $T_{\rm c}/N$  | $T_{\rm c}/4 + T_{\rm c}/N$                |  |

| 4    | $T_{ m c}/N$  | $T_{\rm c}/N$  | $T_{\rm c}/4\sim 2T_{\rm c}/N+T_{\rm c}/4$ |  |

| 5    | $T_{\rm c}/N$ | $T_{\rm c}/N$  | $\leq 3T_c/(2N)$                           |  |

不对称规则采样的采样周期为  $T_c/2$ ,引入的延时为对称规则采样的一半,该方法实现简单,可直接用 DSP 实现,对 DSP 的计算速度要求也不高,适用于对系统延时要求不高的场合。该方法目前应用较多。

改进不对称规则采样的采样周期与不对称规则采样相同,也为 $T_c/2$ ,但该方法必须保证采样和计算的过程在 $T_c/N$ 内完成,提高了对计算速度的要求,其引入的延时随N的增大而减小。该方法不宜直接用DSP实现,可用DSP结合FPGA的方法实现。

多次采样固定更新引入的延时接近于改进不对 称规则采样,可采用 DSP 实现,但同样对计算速度 有较高的要求。

多次采样立即更新引入的延时最小,适用于对延时要求非常高的场合。该方法不宜采用 DSP 实现,可采用 DSP 结合 FPGA 的方法来实现,除了对计算速度要求较高外,还必须对脉冲竞争现象进行消除。

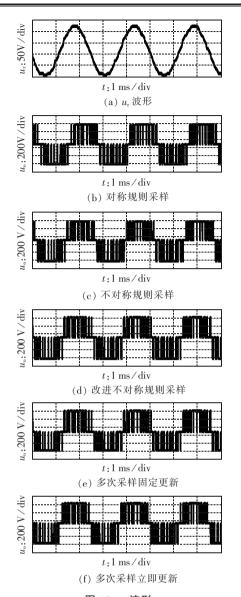

### 5 实验验证

利用 DSP 和 FPGA,同时采用 5 种方法生成 H 桥 变换器的 SPWM 波形。使用相同的正弦参考信号和 载波信号,正弦信号频率 400 Hz,载波频率 8 kHz。采用 DSP 产生正弦信号,1 个基波周期内采样 1 000点,送到 FPGA。在 FPGA 内通过编程,同时实现这 5 种采样方法。对于改进不对称规则采样、多次采样固定更新、多次采样立即更新,N 都取 10。各种方法引入的延时  $t_{\rm d}$  及相位滞后  $\Delta\theta$  如表 2 所示,其中  $\Delta\theta$ = 360  $t_{\rm d}$   $f_{\rm o}$

在 FPGA 的输出端口,通过数据采集系统得到 5 种方法的  $u_{\text{gl}}$  波形,如图 9 所示。通过计算分析,可得

表 2 5 种方法的延时和滞后相位

Tab.2 Time delay and lagging phase of five SPWM methods

| 采样方法 | $t_{ m d}$                       | 实测 ugl         | Δθ/(°) |                |

|------|----------------------------------|----------------|--------|----------------|

|      |                                  | 相位 θ/(°)       | 计算值    | 实测值            |

| 1    | $3T_{\rm c}/2$                   | $37 \pm 0.5$   | 54     | 53.8 ± 0.2     |

| 2    | $3T_{\rm c}/4$                   | $64 \pm 0.5$   | 27     | $26.8 \pm 0.2$ |

| 3    | $7T_{\rm c}/20$                  | $78.5 \pm 0.5$ | 12.6   | $12.4 \pm 0.2$ |

| 4    | $T_{\rm c}/4{\sim}9T_{\rm c}/20$ | $79 \pm 0.5$   | 9~16.2 | $10.5 \pm 0.2$ |

| 5    | $\leq 3T_{\rm c}/20$             | $89 \pm 0.5$   | ≤5.4   | $1.8 \pm 0.2$  |

图 9  $u_{\rm gl}$  脉冲波形 Fig.9 Waveforms of  $u_{\rm el}$  pulse

每种情况下的基波相位  $\theta$  如表 2 所示。可见,各方法间的相位差与理论分析一致。

为了更直接地比较各种方法相对于参考信号引起的相位滞后,通过 FPGA 的嵌入式软件 SignalTap,读取 FPGA 输出端口的脉冲信号,根据式(1)得到 5种情况下的  $u_{o}$  波形,然后把它们与参考正弦信号  $u_{r}$  相比较,如图 10 所示。通过计算分析,可得参考信号与各波形基波的相位差  $\Delta\theta$ ,如表 2 所示,存在  $\pm$  0.2°的波动,可能是由截断和舍入误差引起。对称规则采样、不对称规则采样、改进不对称规则采样的实测平均值与理论分析值相比减少约 0.2°,这是因为参考信号是每个基波周期采样 1000 点所得,由式(4)可知该信号与采样前相比已滞后  $0.18^{\circ}$ ;多次采样固定

图 10  $u_o$  波形 Fig.10 Waveforms of  $u_o$

更新、多次采样立即更新的实测值也在理论分析的取值范围内。实验结果验证了理论分析的正确性。

# 6 结论

对称规则采样、不对称规则采样 SPWM 容易实现,但引入延时较大,在大功率场合开关频率较低的情况下,不利于系统控制性能的提高;改进的不对称规则采样、多次采样固定更新和多次采样立即更新 SPWM 引入的延时较小,但对处理器的计算速度要求较高。本文对这 5 种方法的延时进行了分析,给出了它们的延时时间,为大功率逆变器的设计提供了依据。最后,通过实验验证了理论分析的正确性。

## 参考文献:

[1] 余勇,张兴,季建强,等. 大功率电流型多重化变频电源系统控制与分析[J]. 中国电机工程学报,2004,24(12):24-28.

YU Yong, ZHANG Xing, JI Jianqiang, et al. Control and analysis

- of high-power current source multi-converter power system [J]. Proceedings of the CSEE,2004,24(12):24-28.

- [2] 张强,张崇巍,张兴,等. 风力发电用大功率并网逆变器研究[J]. 中国电机工程学报,2007,27(16):54-59. ZHANG Qiang,ZHANG Chongwei,ZHANG Xing,et al. Study on grid-connected inverter used in high-power wind generation system

grid-connected inverter used in high-power wind generation system [J]. Proceedings of the CSEE,2007,27(16):54-59.

- [3] 谢孟,蔡昆,胜晓松,等. 400 Hz 中频单相电压源逆变器的输出控制及其并联运行控制[J]. 中国电机工程学报,2006,26(6):78-82. XIE Meng,CAI Kun,SHENG Xiaosong,et al. Output control and parallel operation control of 400 Hz single-phase voltage-source inverter[J]. Proceedings of the CSEE,2006,26(6):78-82.

- [4] 李子欣,王平,李耀华,等. 采用数字控制的 400 Hz 大功率逆变电源[J]. 中国电机工程学报,2009,29(6):36-42. LI Zixin,WANG Ping,LI Yaohua,et al. 400 Hz high-power voltage-source inverter with digital control[J]. Proceedings of the CSEE, 2009,29(6):36-42.

- [5] 蔡昆,李耀华,胜晓松,等. 高性能单相电压源逆变器的输出控制 [J]. 电工技术学报,2005,20(1):104-107. CAI Kun,LI Yaohua,SHENG Xiaosong,et al. Output control of

- CAI Kun, LI Yaohua, SHENG Xiaosong, et al. Output control of the high performance single-phase voltage-source inverters [J]. Transactions of China Electrotechnical Society, 2005, 20(1):104-107.

- [6] 李剑,康勇,陈坚. 400 Hz 恒压恒频逆变器的一种模糊-重复混合控制方案[J]. 中国电机工程学报,2005,25(9):54-61. LI Jian,KANG Yong,CHEN Jian. A hybrid fuzzy-repetitive control scheme for 400 Hz CVCF inverters[J]. Proceedings of the CSEE, 2005,25(9):54-61.

- [7] 葛红娟, 蒋华, 王培强. 基于内模原理的新型三相航空静止变流器闭环控制系统[J]. 电工技术学报,2006,21(9):88-92. GE Hongjuan, JIANG Hua, WANG Peiqiang. A novel three-phase aviation static inverter closed-loop control system based on the internal model principle[J]. Transactions of China Electrotechnical Society,2006,21(9):88-92.

- [8] 唐诗颖,彭力,康勇. 脉宽调制逆变电源数字双环控制技术研究 [J]. 中国电机工程学报,2009,29(15):55-60.

TANG Shiying,PENG Li,KANG Yong. Research on dual-loop digital control technique for pulse width modulation inverters[J]. Proceedings of the CSEE,2009,29(15):55-60.

- [9] 单鸿淘,彭力,孔雪娟,等. 数字化过程对脉宽调制逆变电源性能的影响机理[J]. 中国电机工程学报,2009,29(6):29-35. SHAN Hongtao,PENG Li,KONG Xuejuan,et al. Effect of digital process on the performance of pulse width modulation inverter [J]. Proceedings of the CSEE,2009,29(6):29-35.

- [10] HENG Deng, ORUGANTI R, SRINIVASAN D. PWM methods to handle time delay in digital control of a UPS inverter [J]. IEEE

- Power Electronics Letters, 2005, 3(1):1-6.

- [11] 杨水涛,张帆,钱照明. 基于 DSP 的有效消除数字控制延时的 UPS 逆变器多环控制策略 [J]. 电工技术学报,2008,23(12): 84-91

- YANG Shuitao,ZHANG Fan,QIAN Zhaoming DSP-based multiple-loop control strategy for ups inverters with effective control delay elimination [J]. Transactions of China Electrotechnical Society, 2008, 23(12):84-91.

- [12] 李建林,王立乔,李彩霞,等. 基于现场可编程门阵列的多路 PWM 波形发生器[J]. 中国电机工程学报,2005,25(10):55-59. LI Jianlin,WANG Liqiao,LI Caixia,et al. Multi-PWM pulse generator based FPGA[J]. Proceedings of the CSEE,2005,25 (10):55-59.

- [13] 郑飞,费树岷,周杏鹏. 基于 DSP 和 FPGA 的光伏并网控制器设计与实现[J]. 电力自动化设备,2011,31(2):84-89.

ZHENG Fei,FEI Shumin,ZHOU Xingpeng. Design and implementation of photovoltaic grid-connection controller based on DSP and FPGA[J]. Electric Power Automation Equipment,2011,31 (2):84-89.

- [14] 郑飞,费树岷,周杏鹏,等. 基于 DSP 和 FPGA 的 SVPWM 算法及 其在变频调速中的应用[J]. 电力自动化设备,2010,30(11):61-64. ZHENG Fei,FEI Shumin,ZHOU Xingpeng,et al. SVPWM algorithm based on DSP & FPGA and its application in variable frequency drives [J]. Electric Power Automation Equipment, 2010,30(11):61-64.

- [15] 陈增禄,毛惠丰,周炳根,等. SPWM 数字化自然采样法的理论及应用研究[J]. 中国电机工程学报,2005,25(13):32-37. CHEN Zenglu,MAO Huifeng,ZHOU Binggen,et al. A study on theory and application of digital natural sampling based SPWM [J]. Proceedings of the CSEE,2005,25(13):32-37.

- [16] 毛惠丰,陈增禄,任记达,等. SPWM 数字化自然采样法的理论及脉冲误差分析[J]. 中国电机工程学报,2006,26(9):131-136. MAO Huifeng,CHEN Zenglu,REN Jida,et al. Theory and pulse error study of digital natural sampling based SPWM[J]. Proceedings of the CSEE,2006,26(9):131-136.

#### 作者简介:

刘春喜(1977-),男,河南焦作人,讲师,博士,主要研究方向为电力电子变换器数字控制技术(**E-mail**:lcxboai@126.com)。

# Effect of digital SPWM on system delay

LIU Chunxi<sup>1</sup>, SUN Chi<sup>2</sup>, GAO Ji<sup>1</sup>

(1. Liaoning Technical University, Huludao 125105, China; 2. Naval University of Engineering, Wuhan 430033, China)

Abstract: The time delay caused by SPWM(Sinusoidal Pulse Width Modulation) with symmetrical or asymmetrical sampling is analyzed and three improved SPWM methods are introduced; improved asymmetrical sampling, multiple sampling & fixed updating and multiple sampling & immediate updating. The time delay caused by each improved SPWM method is also analyzed. DSP and FPGA are used to simultaneously generate the SPWM waveforms by five SPWM methods with a common sinusoidal reference signal. The phase difference of each SPWM method between its fundamental and reference is obtained and the time delay caused by each SPWM method is derived, which confirms the effectiveness of theoretical analysis and shows that three improved SPWM methods can reduce the time delay effectively.

Key words: delay; electric inverters; SPWM; symmetrical sampling; asymmetrical sampling