Electric Power Automation Equipment

# 换相电压负序分量对LCC-HVDC输电系统 换相的影响分析及其抑制策略

刘 对,李晓华,蔡泽祥,殷珊珊(华南理工大学 电力学院,广东 广州 510640)

摘要:针对逆变侧交流系统故障下传统的基于电网换相换流器的高压直流(LCC-HVDC)输电系统容易发生换相失败这一问题,推导了换相电压负序分量与锁相环的定量关系,并定性分析了换相电压负序分量对LCC-HVDC输电系统换相的影响。在此基础上提出了一种改进双二阶广义积分器锁相环以抑制多次换相失败。该锁相环首先采用具有分离特性的相序解耦谐振控制器来解耦换相电压的正、负序分量;接着利用双二阶广义积分-正交信号发生器再次分离换相电压的正、负序分量以及消除谐波分量;最后采用正交谐波消除模块滤除低次谐波,提升锁相环的抗干扰能力,完成同步信号的准确提取。仿真结果表明,改进的锁相环具有较好的动态性能与较强的换相电压负序分量与谐波抑制效果;在电网电压不对称、谐波含量较高时仍能够高效地追踪电网电压的频率与相位;并能够减少换相失败的发生概率。

关键词:LCC-HVDC 输电系统;换相电压负序分量;换相失败;锁相环;相序解耦谐振控制器

中图分类号:TM 721.1

文献标志码:A

DOI: 10.16081/j.epae.202112028

# 0 引言

传统的基于电网换相换流器的高压直流(LCC-HVDC)输电系统因具有建设成本相对低、传输容量大、功率调节灵活等优点在电网中得到了大规模应用<sup>[1]</sup>。然而晶闸管器件的半控特性及LCC-HVDC输电系统的正常运行以基波正序换相电压为前提进行分析,这就使得换相失败、多次换相失败可能会在逆变侧交流系统发生故障时出现。此时系统中的电气量会发生剧烈的变化,这将对交直流混联电网的安全稳定运行提出巨大挑战<sup>[2]</sup>。

目前,国内外学者针对LCC-HVDC输电系统换相失败方面的问题做了大量的研究。针对多次换相失败机理研究,文献[3]运用谐波电压-时间面积方法来分析LCC-HVDC输电系统多次换相失败机理,发现导致后续换相失败的主要原因是故障恢复期间的谐波,然而文中并没有给出相应的抑制措施。文献[4]以我国某特高压主变充电为例,说明了励磁涌流导致换流母线畸变从而导致周期性换相失败,但发生故障与励磁涌流所引起的谐波特性存在一定差异。文献[5]通过分析证明,在不对称故障下系统的触发角会表现出周期性波动,从而引发多次换相失

收稿日期:2021-04-02;修回日期:2021-11-01

基金项目:国家自然科学基金委员会-国家电网公司智能电网 联合基金资助项目(U1766213);国家自然科学基金资助项目 (51677073)

Project supported by the Smart Grid Joint Fund of National Natural Science Foundation of China & State Grid Corporation of China(U1766213) and the National Natural Science Foundation of China(51677073) 败;并在分析的基础上给出了相应的抑制措施,但没有分析对称故障下系统触发角对LCC-HVDC输电系统换相失败的影响。文献[6]从锁相环的角度出发,指出了传统的同步旋转坐标锁相环(SRF-PLL)在故障下存在的问题并提出抑制多次换相失败的方法,但并未给出故障过程中锁相环受影响的理论分析。

针对换相失败抑制问题,文献[7]采用换相失败 预测控制来抑制 LCC-HVDC 输电系统的换相失败, 然而需要快速地检测电压幅值以及零序分量以实现 该抑制效果。文献[8]提出采用交流量来启动低压 限流环节以达到换相失败抑制的作用,但在直流侧 线路发生故障时该方法没有预想的优势。文献[9] 通过分别在低压限流环节前增加虚拟电阻、电感来 改进启动电压,对抑制多次换相失败有一定的效果, 然而在故障恢复期间虚拟电阻、电感的存在导致恢 复速度较慢。文献[10]从控制的层面进行改进,以 减少换相失败的发生,但这些方法同样需要较高的 检测速度。文献[11]提出采用虚拟换相面积缺乏量 来确定电流的参考值,但该方法受延时条件制约。 此外,换流器拓扑改造[12]、无功补偿装置[13]、改进电 流偏差[14]等方法也可以抑制换相失败。虽然上述方 法可以抑制换相失败,但锁相环的暂态性能对LCC-HVDC输电系统的影响研究较少。文献[15]从畸变 电压对锁相环的影响出发分析了LCC-HVDC输电系 统的运行特性,但在后续分析中认为锁相环锁定的 仍是正序基波电压。

鉴于此,本文基于逆变侧交流系统故障下换相电压负序分量的分析结果,对LCC-HVDC输电系统的锁相环进行改进。首先定量解析了换相电压负序

分量对锁相环的影响;然后结合换相电压-时间面积 方法定性分析了换相电压负序分量对LCC-HVDC输 电系统换相的影响;最后提出了多次换相失败抑制 策略的双二阶广义积分器锁相环(DSOGI-PLL)改进 方法。该方法首先利用具有正、负序分离特性的相 序解耦谐振(SDR)控制器,提取换相电压正序分量 以减少后续低次谐波滤除的负担;然后采用双二阶 广义积分-正交信号发生器(SOGI-QSG)对该正序电 压再次分离并消除谐波;最后应用正交谐波消除模 块(OHCM)滤除低次谐波,从而完成电网电压相位 的快速、准确追踪。在LCC-HVDC输电系统中应用 该锁相环,通过PSCAD/EMTDC仿真验证了所提改 进DSOGI-PLL的快速性与准确性。仿真结果表明, 采用所提改进方法能够减少系统在故障持续期间发 生换相失败的概率,可为多次换相失败的抑制提供 参考。

# 1 换相电压负序分量对 LCC-HVDC 输电系统的影响分析

传统电力系统中一般认为发生对称故障时不存在负序分量(或负序分量较小可以忽略),负序分量仅出现在不对称故障中。然而在LCC-HVDC输电系统中,由于控制系统的作用,在换流母线处发生对称故障时也将出现较大的换相电压负序分量。

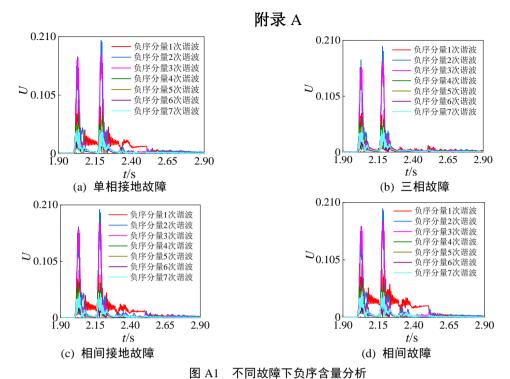

### 1.1 换流母线不同故障下换相电压负序分量的对比

为了验证LCC-HVDC输电系统中逆变侧换流母线对称故障下同样会出现较大的换相电压负序分量,以文献[16]中的CIGRE HVDC模型为例进行说明,分别在单相接地短路、三相短路、相间接地短路、相间短路故障下进行仿真验证。设故障发生时刻为第2s,持续时间为0.5s,接地短路故障和相间故障中的接地电感和相间电感均为0.9H。不同故障下换流母线负序电压低次谐波分量U的分布情况见附录A图A1。

对比图 A1 所示各故障下换流母线负序电压低次谐波分量可以发现,在 LCC-HVDC 输电系统中即使发生对称故障,其 U的含量也基本与发生不对称故障时相持平。同时由于 LCC-HVDC 输电系统的触发、控制以及保护系统大多以正序基波电压为基础进行设计,当系统发生故障时,控制系统的调节作用所产生的换相电压负序分量将导致系统再次出现不平衡量。因此,当交流系统发生故障时,应着重考虑换相电压负序分量对 LCC-HVDC 输电系统的影响。

# 1.2 换相电压负序分量对 LCC-HVDC 输电系统锁相触发的影响分析

根据前文分析,逆变侧交流母线无论发生对称还是非对称故障,LCC-HVDC输电系统换流母线中

换相电压负序电压低次谐波含量均较高。这也表明此时系统的三相电压不平衡程度较高,下面将重点分析三相电压不平衡时对锁相环的影响。设三相不平衡电压 $u_a, u_b, u_c$ 为:

$$\begin{cases} u_{a} = U_{g} \cos \theta_{0} \\ u_{b} = (1+\xi) U_{g} \cos(\theta_{0} - 2\pi/3) \\ u_{c} = (1+\psi) U_{g} \cos(\theta_{0} + 2\pi/3) \end{cases}$$

(1)

式中: $U_g$ 为电网电压幅值; $\xi$ 、 $\psi$ 分别为 b、c 相电压不平衡度; $\theta_0$ 为  $u_a$ 的初相位。根据 Clark 变换,三相电压在 $\alpha\beta$ 坐标系下的表达式为:

$$\begin{cases} u_{\alpha} = U_{g} \cos \theta + A \\ u_{\beta} = U_{v} \sin \theta + B \end{cases} \tag{2}$$

$$\begin{cases} A = U_{g} \left( \frac{\xi + \psi}{6} \cos \theta - \frac{\xi - \psi}{2\sqrt{3}} \sin \theta \right) \\ B = U_{g} \left( \frac{\psi - \xi}{2\sqrt{3}} \cos \theta + \frac{\xi + \psi}{2} \sin \theta \right) \end{cases}$$

(3)

式中: $\theta$ 为 $\alpha$ 轴超前a轴的夹角。由式(2)、(3)可知,A、B为三相电压不平衡量。同样根据 Clark 变换,dq 坐标系下三相电压q轴分量为:

$$u_{q} = U_{g} \sin (\theta - \theta') + U_{g} \frac{\xi + \psi}{3} \sin (\theta - \theta') +$$

$$U_{\rm g} \left[ \frac{\xi + \psi}{6} \sin(\theta + \theta') + \frac{\psi - \xi}{2\sqrt{3}} \cos(\theta + \theta') \right]$$

(4)

式中: $\theta'$ 为d轴超前a轴的夹角。由于 $\theta \approx \theta'$ ,则 $u_q$ 所含有的误差 $\Delta e$ 为:

$$\Delta e = U_{\rm g} \left[ \frac{\xi + \psi}{6} \sin(2\theta) + \frac{\psi - \xi}{2\sqrt{3}} \cos(2\theta) \right]$$

(5)

由式(5)可知:三相电压不平衡将引起一个2倍 频振荡的锁相误差;该误差也将影响锁相环的精度,从而影响LCC-HVDC输电系统的正常运行。

### 1.3 锁相触发对LCC-HVDC输电系统的影响分析

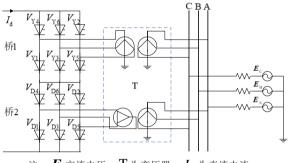

LCC-HVDC 输电系统一般采用 12 脉动换流器,附录 A 图 A2 为 CIGRE HVDC 模型中换流器接线图。CIGRE HVDC 模型中采用 SRF-PLL来跟踪换相电压的相位<sup>[16]</sup>;换流阀  $V_{Y1}-V_{V6}$ 、 $V_{D1}-V_{D6}$ 按照  $V_{Y1}-V_{D1}-V_{Y2}-V_{D2}-\cdots-V_{Y6}-V_{D6}-V_{Y1}-V_{D1}$ 的顺序轮流导通,触发脉冲间隔为 30°。

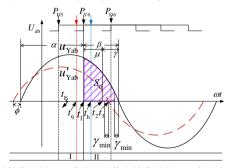

由图 A2 可知,换流阀的换相过程是 2 个换相电路中电感元件能量倒换的过程。因此,换相完成需要足够的电压—时间面积  $S_0$  予以驱动。下面以  $V_{v4}$  向  $V_{v6}$  换相为例定性说明锁相触发对 LCC-HVDC 输电系统的影响,其换相过程见附录 A 图 A3。故障后提前触发时刻  $t_q$ 、滞后触发时刻  $t_h$  提供的最大换相电压时间面积分别记为  $S'_{max}$ 、 $S''_{max}$ ,其表达式如式 (6) 所示。

$$\begin{cases} S'_{\text{max}} = \int_{t_{q}}^{t_{3}} u'_{\text{Yab}} dt \\ S''_{\text{max}} = \int_{t_{b}}^{t_{3}} u'_{\text{Yab}} dt \end{cases}$$

(6)

式中: $u'_{Yab}$ 为故障后换相电压; $t_3$ 为故障后换相失败临界时刻。比较式(6)中的 $S'_{max}$ 、 $S''_{max}$ 与图 A3 所示阴影部分 $S_0$ 可知,触发时刻与换相过程存在一定的关联,而触发时刻的准确与否受锁相环的影响。

由上述分析可知,故障情况下各触发脉冲发生器的输入信号将受到电压不平衡以及谐波的影响,影响LCC-HVDC输电系统的正常换相,进而诱发换相失败<sup>[6]</sup>。研究发现,交流系统故障后LCC-HVDC输电系统的首次换相失败一般难以消除,但在故障未及时消除时,应该降低换相失败在LCC-HVDC输电系统恢复过程中再次发生的概率<sup>[6]</sup>。然而,实际运行中的LCC-HVDC输电系统受换相电压负序分量以及谐波的影响较大。因此,实现快速、准确的锁相触发需首要考虑对换相电压负序分量以及谐波的处理。

### 2 改进的 DSOGI-PLL

基于上述问题,本文提出一种可抑制LCC-HVDC 输电系统多次换相失败的锁相方法。DSOGI-PLL具 有一定滤波功能,故在谐波含量较少时,基波信息 能够被有效提取。然而,当电压不对称或者谐波含 量较高时,DSOGI-PLL同样会受不对称度及谐波的 影响,进而不能较准确地追踪同步信号。因此, DSOGI-PLL需要提升这方面的鲁棒性才能得以广泛 应用。

#### 2.1 SDR 控制器

为了避免负序分量对锁相环的影响,正序分量的有效提取成为三相电压不平衡时需要解决的重要问题。由于SDR控制器具有较好正、负序分量分离的特性,锁相环中可以借鉴这一特性进行设计[17]。SDR控制器正、负序分量分离过程的传递函数 $G_{\text{PSDR}}(s)$ 、 $G_{\text{NSDR}}(s)$ 表达式如式(7)所示。

$$\begin{cases} G_{PSDR}(s) = \frac{k_i \omega_c}{s - j\omega_0 + \omega_c} \\ G_{NSDR}(s) = \frac{k_i \omega_c}{s + j\omega_0 + \omega_c} \end{cases}$$

(7)

式中: $\omega_{\rm e}$ 、 $\omega_{\rm o}$ 分别为截止角频率与谐振角频率; $k_{\rm i}$ 为 SDR 控制器传递函数的阻尼系数。由式(7)可知,在  $\omega_{\rm o}$ 处 SDR 控制器传递函数的增益为 $k_{\rm i}$ ,为了达到正、负序电压分量分离的目的,取 $k_{\rm i}$ =1<sup>[17]</sup>。进而可以得到 SDR 控制器在  $\alpha\beta$ 坐标系下的输出电压正序分量  $\mathbf{u}_{\alpha\beta}^{+} = \left[\mathbf{u}_{\alpha}^{+} \mathbf{u}_{\beta}^{+}\right]$ 、负序分量  $\mathbf{u}_{\alpha\beta}^{-} = \left[\mathbf{u}_{\alpha}^{-} \mathbf{u}_{\beta}^{-}\right]$ 分别为:

$$\begin{cases}

\mathbf{u}_{\alpha\beta}^{+} = \frac{\boldsymbol{\omega}_{c}}{s - j\boldsymbol{\omega}_{0} + \boldsymbol{\omega}_{c}} \mathbf{u}_{\alpha\beta} \\

\mathbf{u}_{\alpha\beta}^{-} = \frac{\boldsymbol{\omega}_{c}}{s + j\boldsymbol{\omega}_{0} + \boldsymbol{\omega}_{c}} \mathbf{u}_{\alpha\beta}

\end{cases} \tag{8}$$

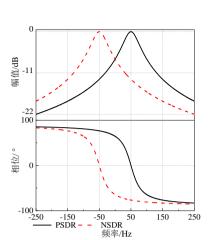

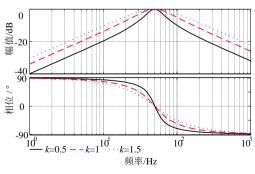

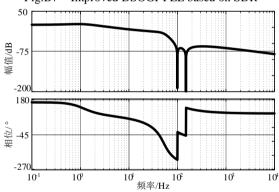

式中:  $\mathbf{u}_{\alpha\beta}$  = [ $\mathbf{u}_{\alpha}$   $\mathbf{u}_{\beta}$ ]为 SDR 控制器在  $\alpha\beta$  坐标系下的输入电压。当 $\omega_0$  = 100 rad /  $\mathbf{s}$ 、 $\omega_c$  = 150 rad /  $\mathbf{s}$  时,传递函数的伯德图如附录 B图 B1 所示。由图可知,SDR 控制器本质上为谐振控制器,基波正序分量可以通过选取适当的  $\omega_c$  来提取。不同  $\omega_c$  ( $\omega_c$  分别为100、150、200 rad /  $\mathbf{s}$ )下正序 SDR 控制器伯德图如附录 B图 B2 所示。对比图 B2 中曲线可知,控制器的带宽、响应速度与参数  $\omega_c$  呈正相关,而增益衰减作用与参数  $\omega_c$  呈负相关。综合考虑本文的  $\omega_c$  取为100 rad /  $\mathbf{s}$ 。另外,通过对式(7)、(8)整理可得:

$$\begin{cases}

\boldsymbol{u}_{\alpha\beta}^{+} = \frac{\boldsymbol{\omega}_{c} \boldsymbol{u}_{\alpha\beta} - \boldsymbol{\omega}_{c} \boldsymbol{u}_{\alpha\beta}^{+} + j\boldsymbol{\omega}_{0} \boldsymbol{u}_{\alpha\beta}^{+}}{s} \\

\boldsymbol{u}_{\alpha\beta}^{-} = \frac{\boldsymbol{\omega}_{c} \boldsymbol{u}_{\alpha\beta} - \boldsymbol{\omega}_{c} \boldsymbol{u}_{\alpha\beta}^{-} + j\boldsymbol{\omega}_{0} \boldsymbol{u}_{\alpha\beta}^{-}}{s}

\end{cases}$$

(9)

此时,正、负序分量在 $\alpha\beta$ 坐标系下存在式(10) 所示关系。

$$\begin{cases}

ju_{\alpha}^{+} = -u_{\beta}^{+} \\

ju_{\beta}^{+} = u_{\alpha}^{+} \\

ju_{\alpha}^{-} = u_{\beta}^{-} \\

ju_{\beta}^{-} = -u_{\alpha}^{-}

\end{cases} (10)$$

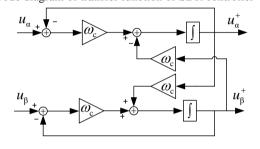

通过式(9)、(10)即可得到SDR控制器的控制结构框图如附录B图B3所示。经上述分析可知,通过SDR控制器后换相电压正、负序分量被解耦,负序分量对输出的正序分量影响将大幅减小。

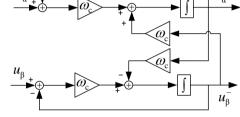

#### 2.2 SGOI-QSG结构

由于 SOGI-QSG 具有一定的滤波功能,在产生 90°相位偏移方面被广泛应用<sup>[18]</sup>,典型的 SGOI-QSG 结构图如附录 B图 B4所示。SGOI-QSG 的输出电压信号 $v'_q(s)$ 及滞后其 90°的输出电压信号 $v'_q(s)$ 对于输入电压信号v(s)的传递函数  $D_1(s)$ 、 $Q_1(s)$ 表达式如式 (11)所示。

$$\begin{cases}

D_{1}(s) = \frac{v'(s)}{v(s)} = \frac{k\omega's}{s^{2} + k\omega's + {\omega'}^{2}} \\

Q_{1}(s) = \frac{v'_{q}(s)}{v(s)} = \frac{k\omega'^{2}}{s^{2} + k\omega's + {\omega'}^{2}}

\end{cases} (11)$$

式中:k为传递函数 $D_1(s)$ 、 $Q_1(s)$ 的阻尼系数; $\omega'$ 为角频率。不同k值下, $D_1(s)$ 、 $Q_1(s)$ 伯德图见附录B图B5。由图可知:SGOI-QSG含有滤波特性;其滤波特性与k值负相关,其动态响应则相反。因此,为兼顾二者的平衡性,取 $k=\sqrt{2^{[18]}}$ 。

#### 2.3 正交谐波消除法

如果在αβ坐标系下 SGOI-QSG 输出基波频率

为 $\hat{\omega}$ 的电压 $v'_{\alpha}$ 、 $v'_{\beta}$ 中分别含有正序电压 $v^*_{\alpha}$ 、 $v^*_{\beta}$ ,负序电压 $v^*_{\alpha}$ 、 $v^*_{\beta}$  以及i次谐波电压 $v^i_{\alpha}$ 、 $v^i_{\beta}$ ,那么 $v'_{\alpha}$ 、 $v'_{\beta}$ 的表达式如式(12)所示。

$$\begin{cases} v_{\alpha}' = v_{\alpha}^{+} + v_{\alpha}^{-} + v_{\alpha}^{i} \\ v_{\beta}' = v_{\beta}^{+} + v_{\beta}^{-} + v_{\beta}^{i} \end{cases}$$

(12)

$v'_{\alpha}, v'_{\beta}$ 的正交信号 $v'_{\alpha\alpha}, v'_{\alpha\beta}$ 表达式为:

$$\begin{cases} v'_{q\alpha} = v^{+}_{\beta} - v^{-}_{\beta} + \frac{1}{i} v^{i}_{\beta} \\ v'_{q\beta} = -v^{+}_{\alpha} + v^{-}_{\alpha} - \frac{1}{i} v^{i}_{\alpha} \end{cases}$$

(13)

正/负序分量计算(PNSC)模块输出电压 $U_{\alpha}^{+}$ 和 $U_{\alpha}^{+}$ 表达式为:

$$\begin{cases} U_{\alpha}^{+} = \frac{1}{2} (v_{\alpha}' - v_{\eta\beta}') = v_{\alpha}^{+} + \frac{1}{2} \left( 1 + \frac{1}{i} \right) v_{\alpha}^{i} \\ U_{\beta}^{+} = \frac{1}{2} (v_{\beta}' + v_{\eta\alpha}') = v_{\beta}^{+} + \frac{1}{2} \left( 1 + \frac{1}{i} \right) v_{\beta}^{i} \end{cases}$$

$$(14)$$

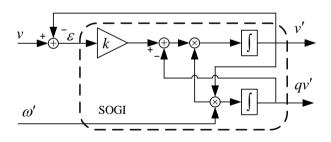

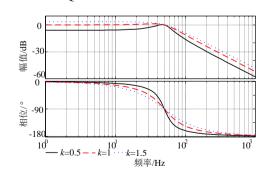

由式(14)可知,SOGI-QSG可以消除输入信号中的负序电压,但并没有抑制i次谐波电压。QHCM首先对谐波电压移相90°构成正交信号,然后再进行消元,可以达到消除谐波的目的。通过对 $U^+_{\alpha}$ 、 $U^+_{\beta}$ 进行微分以实现谐波电压移相90°构成正交信号,即可得到i次谐波电压 $U^-_{\alpha i}$ 、 $U^-_{\beta i}$ 消除的表达式如式(15)所示。

$$\begin{cases}

U_{\alpha i}^{+} = \frac{i}{i-1} \left( U_{\alpha}^{+} - \frac{1}{i} U_{q\beta}^{+} \right) = v_{\alpha}^{+} \\

U_{\beta i}^{+} = \frac{i}{i-1} \left( U_{\beta}^{+} + \frac{1}{i} U_{q\alpha}^{+} \right) = v_{\beta}^{+}

\end{cases} (15)$$

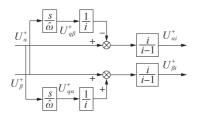

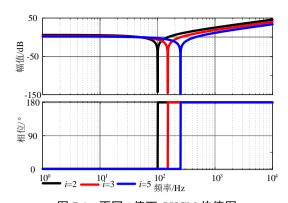

式中:  $U_{q\alpha}^{+}$ 、 $U_{g\beta}^{+}$ 分别为 $U_{\alpha}^{+}$ 和 $U_{\beta}^{+}$ 的正交信号。根据式 (15)可得图 1 所示 QHCM 结构图, 其伯德图见附录 B图 B6。实际应用中为了消除各次谐波通常串联 多个 QHCM。综合考虑,本文采用 2 个 QHCM,分别 消除 2、3 次谐波。

图1 QHCM结构图

Fig.1 Structure diagram of QHCM

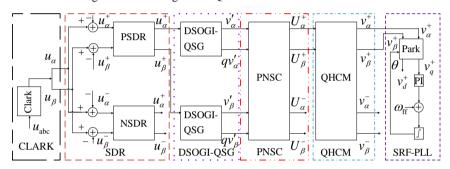

#### 2.4 改进 DSOGI-PLL 结构

改进DSOGI-PLL结构框图如附录B图B7所示。 有较多文献已经对SRF-PLL进行了详细介绍<sup>[19]</sup>,同时PNSC模块为代数运算<sup>[18]</sup>,此处不再对以上2个环节进行介绍。

采集的电压信号首先进行Clark变换;然后依次通过SDR控制器、SOGI-QSG实现正、负序电压分量

的分离并消除部分谐波分量的影响;再经过QHCM 滤除低次谐波电压分量;最后误差信号被输入比例 积分控制器中,实现同步电压的锁相。通过前文分 析可得改进后锁相环的整体伯德图见附录B图B8。

# 3 仿真验证

#### 3.1 改进的DSOGI-PLL性能分析

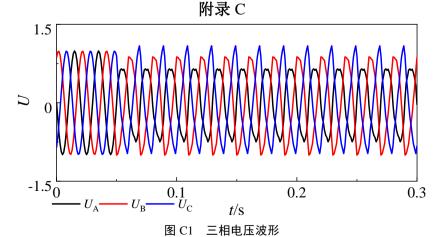

在PSCAD / EMTDC 仿真平台中搭建电力系统, 其由相电压为30 kV 的电源以及有功功率为0.27 MW、 无功功率为-0.1 Mvar 的负载构成。采用谐波注人 的方法来验证不同锁相环的性能。在0.05 s时,电 压幅值跌落至0.8 p.u.,并添加表1所示的各次谐波 电压的正序、负序分量(均为标幺值);同时假设测量 过程中含0.05 p.u.的直流电压分量。附录C图C1为 三相电压波形,由图可知,在0.05 s后三相电压不平 衡且有较大的谐波。

#### 表1 各次谐波电压含量

Table 1 Contents of each harmonic voltage

| 谐波次数 | 含    | 量    | 谐波次数 | 含量   |      |  |

|------|------|------|------|------|------|--|

|      | 正序分量 | 负序分量 | 伯奴仇奴 | 正序分量 | 负序分量 |  |

| 1    | 1.00 | 0.07 | 5    | 0.05 | 0.04 |  |

| 2    | 0.10 | 0.05 | 7    | 0.03 | 0.02 |  |

| 3    | 0.10 | 0.05 |      |      |      |  |

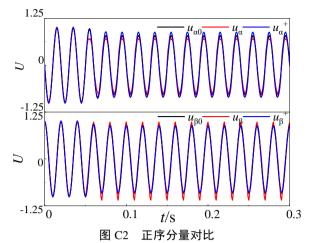

此时三相电压经 Clark 变换得到的  $u_{\alpha}$ 、 $u_{\beta}$ 以及 SDR 控制器输出的  $u_{\alpha}^{+}$ 、 $u_{\beta}^{+}$ 与三相电压经快速傅里叶变换分解得到基波电压后经 Clark 变换得的  $u_{\alpha 0}$ 、 $u_{\beta 0}$ 分量对比如附录 C图 C2 所示。对比图中的曲线可知, $u_{\alpha}$ 、 $u_{\beta}$ 的波形畸变较为严重,而  $u_{\alpha}^{+}$ 、 $u_{\beta}^{+}$ 波形与 $u_{\alpha 0}$ 、 $u_{\beta 0}$ 较为接近,说明 SDR 控制器能够较好地实现正、负序电压分离,从而使输出更加接近基波分量。

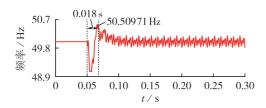

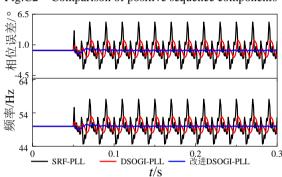

将改进的 DSOGI-PLL 与 SRF-PLL、DSOGI-PLL 进行对比,对比结果如附录C图C3所示。设置锁相 环的比例、积分参数分别为 K,=10、K,=50[6]。根据相 关标准,电力系统应在(50±0.2) Hz的频率范围内波 动,而中、小型容量的系统可在(50±0.5) Hz[20]的频 率范围内波动。对比图 C3 中的结果可以发现,在三 相电压平衡、不含谐波时,3种锁相环输出的相位误 差、频率波动相对较小; 当 a 相电压  $u_a$  跌落至 0.8 p. u.,并注入谐波时,不同锁相环作用下仿真波形出现 较大差异。其中,SRF-PLL、DSOGI-PLL在相位误差 以及频率方面存在较大的误差,无法准确追踪电网 电压。改进的 DSOGI-PLL 由于采用了 SDR 控制器 减少了负序分量对锁相环的影响,同时正交谐波消 除模块也有效地消除了谐波的影响,使改进的DSO-GI-PLL达到较高的锁相精度。图 2 为改进的 DSO-GI-PLL输出频率波形,由图可知其频率在0.018 s后 基本收敛在稳定的波动范围内。

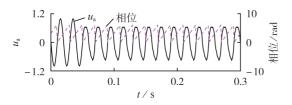

图 3 为改进的 DSOGI-PLL输出相位追踪图,图

#### 图 2 改进的 DSOGI-PLL 输出频率

Fig.2 Output frequency of improved DSOGI-PLL

中 u<sub>a</sub>为标幺值。由图可知:改进的 DSOGI-PLL 无论在电压平衡与否的情况下均可以锁定电压相位;满足精度的同时其在抗干扰力和动态响应速度方面也具有较大的优势。因此,改进的 DSOGI-PLL具有实用性。

图3 改进的DSOGI-PLL输出相位

Fig.3 Output phase angle of improved DSOGI-PLL

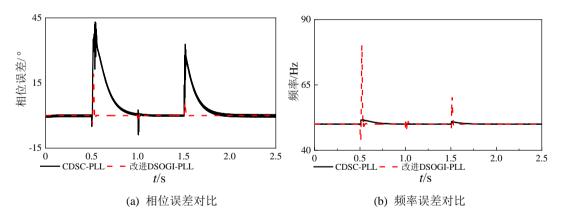

为了验证改进的 DSOGI-PLL 针对不同情况的 适应性,采用PSCAD/EMTDC中自带的锁相环测试 系统进行分析,同时与文献[6]中提及的级联延迟 信号消除法锁相环(CDSC-PLL)进行对比,锁相环比 例积分参数的设置情况与3.1节相同。所搭建的测 试系统由相电压为66 kV的电源以及有功功率为 0.27 MW、无功功率为-0.1 Mvar的负载构成。在 0.5 s时电源电压相位发生90°跳变,1.5 s时发生单 相接地短路故障,并在2s时切除负荷。此时2种锁 相环的相位误差、频率波动对比结果如附录C图C4 所示。对比图中结果可以发现:稳态时2种锁相环输 出的相位误差、频率波动相对较小;当出现相位跳变、 接地短路故障以及切除负荷时,2种锁相环的仿真波 形出现较大的差异,其中CDSC-PLL达到稳定的速度 较慢,其受到的干扰较严重,而改进的DSOGI-PLL可 以有效避免这些情况引发的干扰。

# 3.2 不同锁相触发下LCC-HVDC输电系统运行特性 3.2.1 对比不同锁相环的基本特性

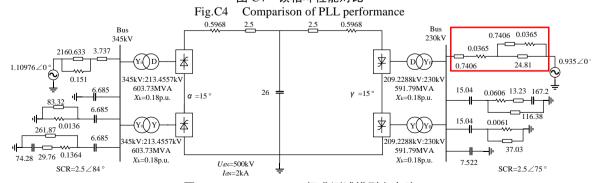

基于 CIGRE HVDC 模型构建的 LCC-HVDC 输电系统仿真模型见附录 C图 C5。设 2种锁相环方案对比分析交流系统发生不同故障后 LCC-HVDC 输电系统的运行特性:方案 1,采用 CIGRE HVDC 模型中锁相环进行仿真;方案 2,将方案 1中锁相环改为改进的 DSOGI-PLL,其参数与 CIGRE HVDC 模型中的锁相环相同。

实际LCC-HVDC输电系统中发生较多的故障为感性故障,且容易诱发换相失败。因此,本文设置2

种经电感 $L_r$ 的接地故障, $L_r$ 大小代表故障的严重程度,具体工况设置如下。

1)工况1:设2s时逆变侧换流母线处发生单相接地故障, $L_r$ =1.1H,持续时间为0.5s。在此工况下,LCC-HVDC输电系统在锁相环方案1、2下逆变侧直流电压 $U_{de}$ 、直流电流 $I_{de}$ 、直流传输功率P以及熄弧角 $\gamma$ 的变化情况如附录C图C6所示,图中 $U_{de}$ 、 $I_{de}$ 及P均为标幺值,后同。由图可知,对于类似较轻故障,采用锁相环方案1、2时LCC-HVDC输电系统均未发生换相失败,且基本不会引起任何不良后果。

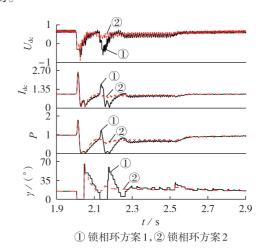

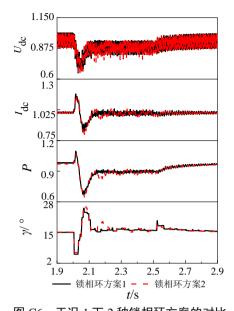

2)工况2:设接地电感为 $L_r$ =0.35H,其余参数设 置情况与工况1相同。在此工况下,LCC-HVDC输 电系统在锁相环方案1、2下逆变侧直流电压、直流 电流、直流传输功率以及熄弧角的变化情况如图4 所示。由图可知, $L_c=0.35$ H时系统的不平衡程度以 及谐波均较为严重,采用锁相环方案1并不能够准 确地检测基波电压相位,影响了触发脉冲的准时性, 导致LCC-HVDC输电系统发生2次换相失败。由于 LCC-HVDC 输电系统控制效果有限,首次换相失败 难以避免,但采用锁相环方案2能有效避免发生多 次换相失败。同时对比图4所示直流传输功率曲线 可以发现,与采用锁相环方案1下的模型相比,采 用锁相环方案2后的LCC-HVDC输电系统直流传输 功率恢复能力更强。这说明改进的 DSOGI-PLL 不 仅可以有效避免LCC-HVDC输电系统发生多次换相 失败,而且对系统在故障后的恢复作用也有一定 帮助。

图4 工况2下2种锁相环方案的对比

Fig.4 Comparison of two PLL schemes in Condition 2

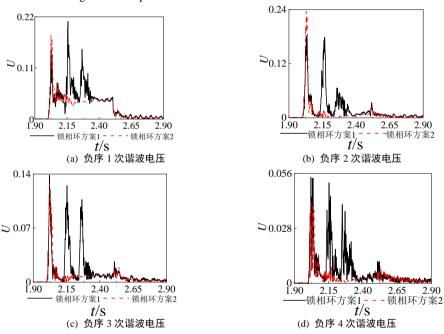

另外,采用锁相环方案1、2时逆变侧换流母线的换相电压负序分量1—4次谐波电压对比情况如附录C图C7所示。由图可知:在故障期间,当采用锁相环方案1时LCC-HVDC输电系统的控制系统在调控的过程中也会产生换相电压负序分量,该换相电压负序分量甚至有可能大于系统故障时产生的换

相电压负序分量;而采用锁相环方案2时,系统仅在故障时存在较大的换相电压负序分量,而在后续故障持续期间换相电压负序分量各次谐波电压含量明显降低,说明改进的DSOGI-PLL有利于LCC-HVDC输电系统控制调节作用,抑制了换相电压负序分量的产生,从而有助于系统的后续换相,减少了多次换相失败发生的概率。

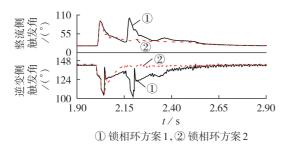

采用锁相环方案1、2时整流、逆变侧触发角的对比情况如图5所示。通过图中的对比曲线可以发现采用锁相环方案1时,在故障情况下整流、逆变侧的触发角将发生多次的剧烈变换,进而导致系统发生多次换相失败;而采用锁相环方案2时,整流、逆变侧的触发角仅在故障时有一次剧烈变化而后快速收敛至稳定值,从而避免发生多次换相失败。这再次说明了改进的DSOGI-PLL能够降低多次换相失败发生的概率。

图 5 2 种锁相环方案下的触发角对比

Fig.5 Comparison of trigger angles between two PLL schemes

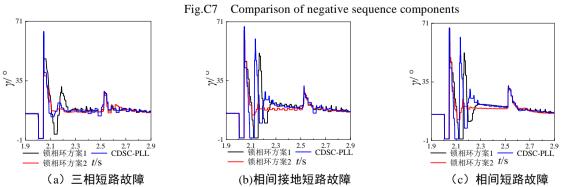

最后,为了验证改进的DSOGI-PLL在LCC-HVDC输电系统中应对其他故障类型的控制效果。在工况2的基础上改变系统的故障类型,同时加入文献[6]提及的CDSC-PLL进行对比分析。在三相短路、相间接地短路、相间短路故障下LCC-HVDC输电系统熄弧角的变化如附录C图C8所示。对比图5及图C8可以发现,改进的DSOGI-PLL在不同故障类型下均具有波动抑制效果,对系统换相具有一定的改善作用,而CDSC-PLL在相间接地短路故障及相间短路故障类型下的改善效果较弱。

#### 3.2.2 对比不同故障水平下锁相环的控制特性

定义故障水平 $f_{\text{RL}}$ 表示系统故障的严重程度 $^{[1]}$ ,其表达式如式 $^{(16)}$ 所示。

$$f_{\rm FL} = \frac{U_{\rm N}^2}{\omega L_{\rm f} P_{\rm N}} \times 100 \% \tag{16}$$

式中: $U_{N}$ 、 $\omega$ 分别为额定电压、额定角频率; $P_{N}$ 为额定功率。

设故障发生时刻为第2s,持续时间为0.5s。在单相接地短路、三相短路、相间接地短路以及相间短路故障下根据式(16)进行故障水平计算,不同故障水平下采用锁相环方案1、2时换相失败次数如附录

C表C1所示。由表可知:在不同故障类型下,故障持续期间采用锁相环方案1后LCC-HVDC输电系统发生多次换相失败;而采用锁相环方案2后仅发生首次换相失败。这说明改进的DSOGI-PLL在故障期间可以对换相电压正、负序分量有效解耦,并消除换相电压负序分量及谐波的影响,快速地追踪电网电压的频率与相位,为LCC-HVDC输电系统提供准确、可靠的触发信号。

#### 3.2.3 对比不同短路比下锁相环的控制特性

调整逆变侧交流系统的阻抗以提高系统短路比,进一步验证改进的DSOGI-PLL在LCC-HVDC输电系统中的控制效果。设附录 C图 C5 方框中系统等效串联阻抗为  $R=2.7383\Omega$ 、L=0.0325H,此时系统的短路比为 5。不同故障水平下锁相环方案 1.2下 LCC-HVDC输电系统的换相失败次数如附录 C表 C2 所示。

对比表C1及表C2可以发现,系统短路比增大后LCC-HVDC输电系统发生多次换相失败的次数有所减少,但当短路比为5时LCC-HVDC输电系统在采用锁相环方案1时仍然会出现多次换相失败,而采用锁相环方案2时未出现该情况,再次验证了改进的DSOGI-PLL能够降低多次换相失败发生的概率。

# 4 结论

针对LCC-HVDC输电系统在逆变侧故障时容易发生换相失败的问题,本文基于逆变侧交流系统故障下换相电压负序分量的分析结果,提出了一种改进的DSOGI-PLL,并验证了其控制效果,所得结论如下:

- 1)改进的 DSOGI-PLL 的动态响应效果好,其在 负序、谐波抑制方面具有较大的优势;

- 2)当电网电压不平衡及谐波含量较高时,改进的 DSOGI-PLL仍能够高效地追踪电网电压的频率与相位:

- 3)由于改进的DSOGI-PLL在负序分量以及谐波抑制方面具有较好的鲁棒性,将其应用于LCC-HVDC输电系统中可以有效降低多次换相失败的发生概率,进而为实际工程中多次换相失败的抑制提供参考。

本文研究了换相电压负序分量对LCC-HVDC输电系统底层锁相触发控制环节的影响,换相电压负序分量还会对LCC-HVDC输电系统其他控制环节造成不利影响,后续将进行深入研究。

附录见本刊网络版(http://www.epae.cn)。

# 参考文献:

[1] 景柳铭,王宾,董新洲,等. 高压直流输电系统连续换相失败研

- 究综述[J]. 电力自动化设备,2019,39(9):116-123.

- JING Liuming, WANG Bin, DONG Xinzhou, et al. Review of consecutive commutation failure research for HVDC transmission system[J]. Electric Power Automation Equipment, 2019, 39(9):116-123.

- [2] 周泓宇,李培平,姚伟,等. 抑制直流后续换相失败的电化学储能有功控制策略[J]. 电力系统自动化,2021,45(19):70-78. ZHOU Hongyu,LI Peiping,YAO Wei,et al. Active power control strategy of electrochemical energy storage for mitigating subsequent DC commutation failures[J]. Automation of Electric Power Systems,2021,45(19):70-78.

- [3] 王峰,刘天琪,周胜军,等. 谐波对HVDC系统换相失败的影响机理及定量分析方法[J]. 中国电机工程学报,2015,35 (19):4888-4894.

- WANG Feng, LIU Tianqi, ZHOU Shengjun, et al. Mechanism and quantitative analysis method for HVDC commutation failure resulting from harmonics[J]. Proceedings of the CSEE, 2015, 35(19):4888-4894.

- [4] 李新年,陈树勇,李涛,等. 特高压主变充电导致直流周期性换相失败的原因[J]. 电网技术,2014,38(10):2671-2679.

- LI Xinnian, CHEN Shuyong, LI Tao, et al. Research on the periodic commutation failure by 1000 kV UHV transformer energizing for LinFeng HVDC project[J]. Power System Technology, 2014, 38(10):2671-2679.

- [5] 曾亮,李永丽,张云柯,等. 逆变侧交流系统不对称故障引发 HVDC 系统连续换相失败的机理及抑制策略研究[J]. 中国电机工程学报,2019,39(11):3159-3168.

- ZENG Liang, LI Yongli, ZHANG Yunke, et al. Research on mechanism and control strategy of continuous commutation failures in HVDC system caused by asymmetrical fault in inverter-side AC system[J]. Proceedings of the CSEE, 2019, 39 (11):3159-3168.

- [6] WANG Juanjuan, GONG Yingming, FU Chuang, et al. A novel phase-locked loop for mitigating the subsequent commutation failures of LCC-HVDC systems[J]. IEEE Transactions on Power Delivery, 2021, 36(3):1756-1767.

- [7] YAO Wei, LIU Chang, FANG Jiakun, et al. Probabilistic analysis of commutation failure in LCC-HVDC system considering the CFPREV and the initial fault voltage angle[J]. IEEE Transactions on Power Delivery, 2020, 35(2):715-724.

- [8] 李瑞鹏,李永丽,陈晓龙,等. 一种抑制直流输电连续换相失败的控制方法[J]. 中国电机工程学报,2018,38(17):5029-5042,5300

- LI Ruipeng, LI Yongli, CHEN Xiaolong, et al. A control method for suppressing the continuous commutation failure of HVDC transmission[J]. Proceedings of the CSEE, 2018, 38 (17):5029-5042,5300.

- [9] 郭春义,李春华,刘羽超,等. 一种抑制传统直流输电连续换相 失败的虚拟电阻电流限制控制方法[J]. 中国电机工程学报, 2016,36(18):4930-4937,5117.

- GUO Chunyi, LI Chunhua, LIU Yuchao, et al. A DC current limitation control method based on virtual-resistance to mitigate the continuous commutation failure for conventional HVDC [J]. Proceedings of the CSEE, 2016, 36(18):4930-4937, 5117.

- [10] MIRSAEIDI S, DONG X Z, TZELEPIS D, et al. A predictive control strategy for mitigation of commutation failure in LCCbased HVDC systems [J]. IEEE Transactions on Power Electronics, 2019, 34(1):160-172.

- [11] 刘磊, 林圣, 何正友. 基于虚拟换相面积缺乏量的 HVDC 系统 连续换相失败抑制策略[J]. 中国电机工程学报, 2018, 38(18):

- 5361-5368.

- LIU Lei, LIN Sheng, HE Zhengyou. A novel method based on virtual commutation area insufficient to mitigate the continuous commutation failure for HVDC[J]. Proceedings of the CSEE, 2018, 38(18):5361-5368.

- [12] XUE Ying, ZHANG Xiaoping, YANG Conghuan. Elimination of commutation failures of LCC HVDC system with controllable capacitors [J]. IEEE Transactions on Power Systems, 2016, 31 (4):3289-3299.

- [13] LEI Y K, LI T, TANG Q, et al. Comparison of UPFC, SVC and STATCOM in improving commutation failure immunity of LCC-HVDC systems[J]. IEEE Access, 2020, 8:135298-135307.

- [14] 夏海涛,周小平,洪乐荣,等.一种抑制后续换相失败的自适应电流偏差控制方法[J].中国电机工程学报,2019,39(15):4345-4356.

- XIA Haitao, ZHOU Xiaoping, HONG Lerong, et al. An adaptive current deviation control method for suppressing following commutation failures[J]. Proceedings of the CSEE, 2019, 39(15):4345-4356.

- [15] 郭紫昱,林涛,王立永,等. 逆变侧交流电压畸变下 HVDC 运行特性分析[J]. 电力自动化设备,2017,37(8):150-157.

GUO Ziyu,LIN Tao,WANG Liyong,et al. Influence of inverter-side AC-voltage distortion on HVDC system[J]. Electric Power Automation Equipment,2017,37(8):150-157.

- [16] BAGHERI-VANDAEI A, FILIZADEH S. Generalised extended-frequency dynamic phasor model of LCC-HVDC systems for electromagnetic transient simulations[J]. IET Generation, Transmission & Distribution, 2018, 12(12):3061-3069.

- [17] 李林,郭源博,张晓华. 复杂电网工况下基于 CDSOGI-SPLL 的 电网电压同步方法[J]. 电力系统自动化,2017,41(16):151-157. LI Lin, GUO Yuanbo, ZHANG Xiaohua. Synchronization method of grid voltage based on CDSOGI-SPLL under complex power grid conditions[J]. Automation of Electric Power Systems,2017,41(16):151-157.

- [18] 涂娟,汤宁平. 基于改进型 DSOGI-PLL的电网电压同步信号检测[J]. 中国电机工程学报,2016,36(9):2350-2356.

TU Juan, TANG Ningping. Synchronizing signal detection for grid voltage based on modified DSOGI-PLL[J]. Proceedings of the CSEE,2016,36(9):2350-2356.

- [19] 胡彬,吴超,年珩,等. 薄弱电网下新能源设备并网锁相同步方式综述[J]. 电力自动化设备,2020,40(9);26-34,41.

HU Bin, WU Chao, NIAN Heng, et al. Overview of phase-locked synchronization methods of renewable energy equipment in weak and distorted grid[J]. Electric Power Automation Equipment,2020,40(9);26-34,41.

- [20] 国家技术监督局. 电能质量电力系统频率允许偏差:GB/T 15945—1995[S]. 北京:中国标准出版社,2004.

### 作者简介:

刘对

刘 对(1990—), 男, 湖北襄阳人, 博士研究生, 主要研究方向为高压直流输电故障分析及控制(E-mail: 201710101807@mail.scut.edu.cn);

李晓华(1975—),女,湖北黄石人,教授,博士研究生导师,博士,通信作者,主要研究方向为电力系统故障分析与继电保护、直流输电控制与保护(E-mail:eplxh@scut.edu.cn)。

(编辑 王欣竹)

# Influence analysis of negative sequence components of commutation voltage on commutation of LCC-HVDC transmission system and its suppression strategy

LIU Dui, LI Xiaohua, CAI Zexiang, YIN Shanshan

(School of Electric Power Engineering, South China University of Technology, Guangzhou 510640, China)

Abstract: Aiming at the problem that LCC-HVDC (Line Commutated Converter based High Voltage Direct Current) transmission system may have commutation failure when the AC system fault occurs on the inverter side, the quantitative relationship between the negative sequence components of the commutation voltage and PLL(Phase Locked Loop) is deduced, and the influence of the negative sequence component of the commutation voltage on the commutation of LCC-HVDC transmission system is qualitatively analyzed. On this basis, an improved double second-order generalized integrator PLL is proposed to suppress multiple commutation failures. Firstly, the phase sequence decoupled resonant controller with separation characteristics is used to decouple the positive and negative components of commutation voltage. Then, using the double second-order generalized integrator-quadrature signal generator, the positive and negative sequence components are separated, and harmonic components are eliminated again. Finally, the quadrature harmonic cancellation module is used to filter the low-order harmonics, improve the anti-interference ability of PLL, and complete the accurate extraction of the synchronization signal. Simulative results show that the improved PLL has better dynamic performance and a strong suppression capability of negative sequence components of commutation voltage and harmonic. The frequency and phase of the grid voltage can be captured efficiently when the grid voltage is asymmetric and the harmonic content is high. And the improved PLL can reduce the probability of commutation failure.

**Key words:** LCC-HVDC transmission system; negative sequence components of commutation voltage; commutation failure; phase locked loops; phase sequence decoupled resonant controller

.....

(上接第17页 continued from page 17)

# Optimal configuration of integrated energy system equipment considering reliability value

GAO Xueqian, LIU Wenxia

(State Key Laboratory of Alternate Electrical Power System with Renewable Energy Sources, North China Electric Power University, Beijing 102206, China)

Abstract: In order to promote the power grid and terminal DIES (Distributed Integrated Energy System) to share the responsibility of the users' energy supply reliability by market mechanism, and fully reflect the reliability value of DIES, an optimal configuration method of integrated energy system equipment considering reliability value is proposed. Based on the electricity price of node considering reliability and the reliability evaluation of DIES, a grid-connected electricity price estimation model considering reliability for DIES is constructed. Based on this, a two-layer collaborative planning model that takes into account optimal configuration and operation of equipment is established. The equipment capacity allocation with the goal of optimizing the total revenue of DIES is performed in the upper layer. Considering incremental value of reliability, the output of each unit is optimized with the goal of maximizing operating revenue in the lower layer. An example is used to verify the effectiveness of the optimal configuration model of integrated energy system considering reliability value, and the impacts of users' load characteristics, users' energy supply reliability requirements, and annual load growth rate of distribution network on the configuration results are analyzed.

**Key words:** integrated energy system; electricity price of node; reliability value; ISODATA clustering; adaptive differential evolution algorithm; collaborative optimal configuration

Fig.A1 Analysis of negative sequence components under different faults

注:  $\boldsymbol{E}$  交流电压; T 为变压器;  $I_{d}$  为直流电流。

#### 图 A2 12 脉动换流器接线图 Fig.A2 Wiring diagram of 12 pulse converter

注: $t_1$  为触发脉冲  $P_{Y6}$  的触发时刻; $t_2$  为故障前换相结束时刻; $t_3$  为故障后换相失败临界时刻; $\alpha$  为触发延迟角; $\mu$  为换相角; $\gamma$  为熄弧角; $\beta$  为触发超前角; $\gamma_{\min}$  为最小熄弧角; $\phi$  为相位超前角; $u_{Yab}$  为故障前换相电压; $u_{Yab}'$  为故障后换相电压; $t_F$  为故障时刻; $t_q$  为触发提前时刻; $t_h$  为触发滞后时刻。

### 图 A3 锁相触发对换相影响示意图

Fig.A3 Schematic diagram of influence of phase-locked trigger on commutation

附录 B

图 B1 SDR 控制器传递函数的伯德图

Fig.B1 Bode diagram of transfer function of SDR controller

图 B2 不同  $\omega_c$ 下正序 SDR 控制器伯德图

Fig.B2 Bode diagram of SDR controller under different  $\omega_c$   $u_a \quad \boxed{v_a}$

(a) 正序 SDR 控制器结构图

(b) 负序 SDR 控制器结构图

图 B3 SDR 控制器结构图 Fig.B3 Structure diagram of SDR controller

图 B4 SOGI-QSG 示意图 Fig.B4 Schematic diagram of SOGI-QSG

(a) 不同 k 值下  $D_1(s)$ 伯德图

(b) 不同 k 值下  $Q_1(s)$ 伯德图

图 B5 不同 k 值下  $D_1(s)$ 、 $Q_1(s)$ 伯德图

Fig.B5 Bode diagram of  $D_1(s)$  and  $Q_1(s)$  under different k values

图 B6 不同 i 值下 QHCM 伯德图 Fig.B6 Bode diagram of QHCM under different i values

图 B7 基于 SDR 控制器改进的 DSOGI-PLL Fig.B7 Improved DSOGI-PLL based on SDR

图 B8 改进后锁相环伯德图 Fig.B8 Bode diagram of improved PLL

Fig.C1 Waveforms of three phase voltage

Fig.C2 Comparison of positive sequence components

图 C3 锁相环仿真测试对比

Fig.C3 Simulation test comparison of PLL

# 图 C4 锁相环性能对比

图 C5 CIGRE HVDC 标准测试模型主电路 Fig.C5 Main circuit of CIGRE HVDC benchmark model

图 C6 工况 1 下 2 种锁相环方案的对比 Fig.C6 Comparison of two PLL schemes under Condition 1

图 C7 负序分量的对比

图 C8 不同故障下采用 3 种锁相环方案时的  $\gamma$  波形 Fig.C8 Waveforms of  $\gamma$  with three PLL schemes under different faults

# 表 C1 不同故障下 2 种锁相环方案下换相失败的次数对比

Table C1 Comparison of commutation failure times with two PLL schemes under different faults

|                | $L_{ m f}/{ m H}$ | 换相失败次数 |         |   |   |   |         |   |   |

|----------------|-------------------|--------|---------|---|---|---|---------|---|---|

| $f_{ m FL}/\%$ |                   |        | 锁相环方案 1 |   |   |   | 锁相环方案 2 |   |   |

|                |                   | 1      | 2       | 3 | 4 | 1 | 2       | 3 | 4 |

| 15             | 1.123             | 0      | 2       | 2 | 2 | 0 | 1       | 1 | 1 |

| 20             | 0.842             | 2      | 2       | 2 | 2 | 1 | 1       | 1 | 1 |

| 25             | 0.674             | 2      | 2       | 2 | 2 | 1 | 1       | 1 | 1 |

| 30             | 0.561             | 2      | 1       | 2 | 2 | 1 | 1       | 1 | 1 |

| 35             | 0.481             | 2      | 1       | 2 | 2 | 1 | 1       | 1 | 1 |

| 40             | 0.421             | 2      | 1       | 2 | 2 | 1 | 1       | 1 | 1 |

| 45             | 0.374             | 2      | 1       | 2 | 2 | 1 | 1       | 1 | 1 |

| 50             | 0.337             | 2      | 1       | 1 | 1 | 1 | 1       | 1 | 1 |

| 55             | 0.306             | 2      | 1       | 3 | 3 | 1 | 1       | 1 | 1 |

| 60             | 0.281             | 3      | 1       | 3 | 2 | 1 | 1       | 1 | 1 |

| 65             | 0.259             | 3      | 1       | 4 | 2 | 1 | 1       | 1 | 1 |

| 70             | 0.241             | 1      | 1       | 1 | 1 | 1 | 1       | 1 | 1 |

| 75             | 0.225             | 1      | 1       | 1 | 1 | 1 | 1       | 1 | 1 |

| 80             | 0.210             | 2      | 1       | 1 | 1 | 1 | 1       | 1 | 1 |

| 85             | 0.198             | 2      | 1       | 1 | 1 | 1 | 1       | 1 | 1 |

注: ①代表单相接地短路故障; ②代表三相短路故障;

③代表相间接地短路故障; ④代表相间短路故障

表 C2 不同短路比下 2 种锁相环方案下换相失败的次数对比

Table C2 Comparison of commutation failure times with two PLL schemes under different SCR

|                 | $L_{ m f}/{ m H}$ | 换相失败次数 |   |   |   |         |   |   |   |

|-----------------|-------------------|--------|---|---|---|---------|---|---|---|

| $f_{\rm FL}/\%$ |                   | 锁相环方案1 |   |   |   | 锁相环方案 2 |   |   |   |

|                 |                   | 1      | 2 | 3 | 4 | 1       | 2 | 3 | 4 |

| 20              | 0.842             | 0      | 0 | 0 | 1 | 0       | 0 | 0 | 0 |

| 25              | 0.674             | 0      | 1 | 1 | 1 | 0       | 0 | 1 | 1 |

| 30              | 0.561             | 1      | 1 | 1 | 1 | 0       | 1 | 1 | 1 |

| 35              | 0.481             | 1      | 1 | 1 | 1 | 1       | 1 | 1 | 1 |

| 40              | 0.421             | 1      | 1 | 1 | 1 | 1       | 1 | 1 | 1 |

| 45              | 0.374             | 1      | 1 | 1 | 1 | 1       | 1 | 1 | 1 |

| 50              | 0.337             | 1      | 1 | 1 | 1 | 1       | 1 | 1 | 1 |

| 55              | 0.306             | 1      | 1 | 2 | 2 | 1       | 1 | 1 | 1 |

| 60              | 0.281             | 1      | 1 | 1 | 1 | 1       | 1 | 1 | 1 |

| 65              | 0.259             | 1      | 1 | 1 | 1 | 1       | 1 | 1 | 1 |

| 70              | 0.241             | 2      | 1 | 1 | 1 | 1       | 1 | 1 | 1 |

| 75              | 0.225             | 2      | 1 | 1 | 1 | 1       | 1 | 1 | 1 |

| 80              | 0.210             | 1      | 1 | 1 | 1 | 1       | 1 | 1 | 1 |

| 85              | 0.198             | 1      | 1 | 1 | 2 | 1       | 1 | 1 | 1 |

| 90              | 0.187             | 2      | 1 | 2 | 2 | 1       | 1 | 1 | 1 |

注: ①代表单相接地短路故障; ②代表三相短路故障;

③代表相间接地短路故障; ④代表相间短路故障