# 2022年3月

# 基于FPGA的模块化多电平换流器并行化 控制器设计及实验验证

王 宇,刘崇茹,侯延琦,刘昊宇,李庚银 (华北电力大学 新能源电力系统国家重点实验室,北京 102206)

摘要:模块化多电平换流器(MMC)中数以千计的子模块(SM)给控制器计算带来很大负担。海量数据采集、 复杂控制计算以及不同控制器间通信等因素导致整个控制链路延时较长,恶化系统动态特性,甚至导致并网 后系统不稳定。设计了一种基于现场可编程门阵列(FPGA)的集成控制器,在单块FPGA板卡中实现MMC的 全部控制策略。控制器充分发挥FPGA的并行特性,每种控制模块尽可能采用并行设计,并将相互独立的控 制模块并行执行,以提高控制器的计算速度。基于RTDS平台进行了硬件在环实验,对所开发控制器进行功 能验证。结果表明:所开发控制器链路延时短,响应速度快,可用于控制策略开发测试、控制参数调试等

关键词:模块化多电平换流器;控制器;现场可编程门阵列;并行计算;硬件在环

中图分类号:TM 46

文献标志码:A

DOI: 10.16081/j.epae.202112006

# 0 引言

柔性直流输电技术是以可控关断器件和脉宽调 制技术为基础的直流输电技术[1]。其中,模块化多 电平换流器(MMC)克服了二、三电平换流器对开关 一致性的要求,具备开关损耗低、波形质量好等优 势,并可通过增加级联子模块(SM)的方式实现电压 提升和容量扩展,已成为柔性直流输电的首选拓扑, 并在学术界和工业界得到了广泛的研究和应用[2]。

MMC的诸多优势来自于其桥臂采用子模块级 联的独特结构,并通过子模块内部的电容充放电实 现交直流系统间的能量传递。随着柔性直流输电系 统向高电压、大容量方向发展,MMC单相桥臂中串 联子模块个数可高达数百个,且每个子模块均需独 立控制,给MMC控制系统的设计和实现带来诸多 挑战[3]。

实际工程所使用成套设计的控制保护装置结构 复杂,不仅需要实现柔性直流输电系统的基本控制 功能,还需要实现大量测量数据运算、主备切换逻 辑、顺控逻辑、阀控保护逻辑、阀控与每个功率模块 通信逻辑等大量功能,因此控制系统中的测量、极 控、阀控等环节均单独组屏[4]。对于阀组串联型特 高压柔性直流输电系统,还增加了阀组控制。柔性 直流输电系统的控制保护装置数量多,不同控制保 护装置之间通信数据多,控制功能计算占用资源多, 这导致实际工程中实测链路延时高达600~700 μs<sup>[5]</sup>。 长控制链路延时不仅会恶化系统的动态特性,甚至

收稿日期:2021-05-16;修回日期:2021-10-18 基金项目:国家电网公司科技项目(SGTYHT/17-JS-199) Project supported by the Science and Technology Project of SGCC(SGTYHT/17-JS-199)

造成系统并网后出现振荡失稳的风险[6]。

现场可编程门阵列(FPGA)是一种并行架构的 芯片,具备分布式内存、流水线架构以及可扩展的 高速输入输出(IO)口,可以实现快速大规模数据通 信[7]。近年来,以FPGA为计算工具的MMC一次系 统实时仿真技术得到飞速发展,利用FPGA的并行 特性处理众多子模块的等值计算[8-11]。对于控制系 统,现有的柔性直流输电系统控制器大多采用FPGA 驱动 AD 采样,并将测量数据传递给上层数字信号 处理器(DSP),由DSP完成控制计算任务的模式。 文献[12]采用多核 DSP+FPGA 架构,将6个桥臂的 均压控制分布到6个并行运行的核,上层控制单独 占用1个核,且上层控制与桥臂均压控制之间仍采 用串行方式,FPGA只用作端口数据采集与发送的驱 动。随着FPGA制造工艺的提升,其片上集成的数 字信号计算资源也不断增加,使得FPGA在满足快 速数据通信的基础上,还可以进行一些复杂的数字 信号处理,现有MMC控制器设计方案未能充分发挥 FPGA这一优势。

在此背景下,本文设计了一种基于FPGA的MMC 集成控制器,能够实现柔性直流输电系统的基本控 制功能,并充分发挥FPGA并行计算特性,提高控制 器的计算速度。控制器采用单块FPGA板卡实现单 端MMC的各类控制策略,并通过控制模块内并行设 计、控制模块间并行计算的方式减小整个控制计算 耗时。基于RTDS平台构建了201电平的单端MMC 实验测试系统,通过潮流反转实验、开关频率优化实 验、环流抑制器投退实验对所开发控制器的性能进 行验证。

# 91

# 1 MMC控制系统

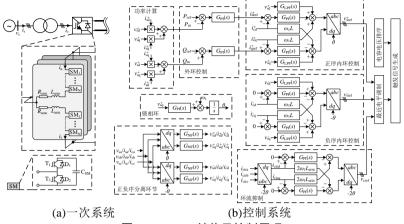

MMC系统结构如附录A图A1所示。图A1(a)为一次系统结构,包含三相6个桥臂,每个桥臂由N个子模块、桥臂电抗器 $L_{arm}$ 和表征损耗的桥臂电阻 $R_{arm}$ 串联组成。目前工程中广泛使用半桥子模块(HBSM),每个子模块由2个IGBT( $T_1$ 、 $T_2$ )及其反并联续流二极管和直流侧储能电容 $C_{SM}$ 组成。子模块接收控制器给出的触发信号在投入( $T_1$ 导通、 $T_2$ 关断)和旁路( $T_1$ 关断、 $T_2$ 导通)状态间切换,在交流侧输出多电平阶梯波,在直流侧维持直流电压恒定。

图 A1(b)为 MMC 控制系统,包括正负序分离环 节、锁相环、功率计算、外环控制、正负序内环控制、 环流抑制、最近电平调制、电容电压排序和触发信号 生成环节。其中后4种环节组成下层控制,工程上 又称之为阀控;其余环节组成上层控制,工程上又称 之为极控。正负序分离环节提取网侧电压、电流和 阀侧电流的正负序分量,其中网侧电压、电流的正序 分量进一步用于计算注入 MMC 的功率,并进入外环 控制。外环控制产生正序电流参考值。负序内环控 制用于抑制电网不平衡或交流侧不对称故障下出现 的负序电流分量。环流抑制用于消除2倍频环流分 量。最近电平调制环节确定每个桥臂需要导通的子 模块个数。电容电压平衡控制用于平衡同一桥臂各 子模块电容电压大小,使其均匀分布。最终触发信 号生成环节产生各个子模块的控制信号,并驱动相 应子模块做出动作。

# 2 控制器并行化设计及 FPGA 实现

由附录A图A1可知,大多数控制功能都可以拆分成加、减、乘、比例积分(PI)环节、低通滤波、陷波滤波、Park 变换及反变换等基本模块,且PI环节、低通滤波、陷波滤波、Park 变换及反变换内部也是由基本的数学计算模块组成的。本文控制器设计采用并行思想,充分发挥FPGA的优势,对每个计算模块采用并行计算设计,同时将相互独立(如外环控制和环流抑制)或功能相同(如6个桥臂的电容电压排序、触发信号生成)的控制模块并行执行,最大幅度减小控制器的计算时间。若无特殊说明,本文控制系统中的数据均为符合IEEE 754标准的单精度浮点数。

## 2.1 PI控制器

PI 控制器是一种常用的线性控制器,根据给定值与实际输出值构成控制偏差,将偏差的比例和积分通过线性组合构成控制量。根据附录 A 图 A1, PI 环节在 MMC 的外环控制、锁相环、正负序内环控制以及环流抑制中均有使用,且锁相环中的积分环节也可以看作是比例系数为 0、积分系数为 1 的 PI 环节。PI 控制器的传递函数  $G_{\text{PI}}(s)$  为:

$$G_{\rm PI}(s) = k_{\rm p} + k_{\rm i}/s \tag{1}$$

式中: $k_p$ 和 $k_i$ 分别为PI环节的比例系数和积分系数。采用双线性(Tustin)变换<sup>[13]</sup>将式(1)从s域转换到z域,则有:

$$y_{\rm PI}(n) = \left(k_{\rm p} + \frac{k_{\rm i}T_{\rm S}}{2}\right)x_{\rm PI}(n) + \frac{k_{\rm i}T_{\rm S}}{2}x_{\rm PI}(n-1) + y_{\rm PI}(n-1) (2)$$

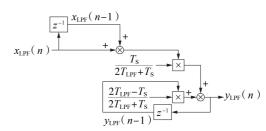

式中:  $T_s$ 为控制周期;  $x_{PI}(n)$  和  $x_{PI}(n-1)$  分别为 PI 环节当前时刻 n 和上一时刻 n-1 的输入信号;  $y_{PI}(n)$  和  $y_{PI}(n-1)$  为 PI 环节当前时刻和上一时刻的输出信号。由式(2)可以得到图 1 所示的 PI 控制器计算框图。PI 控制器的计算分为 3 级: 第一级并行执行 2 个乘法运算; 第二级和第三级分别执行 1 个加法运算,其中第二级运算的结束信号用于第三级计算的起始信号,上一时刻的输入和输出信号通过寄存当前时刻输入和输出信号得到。

$$x_{\text{PI}}(n)$$

$$z^{-1}$$

$$x_{\text{PI}}(n-1)$$

$$x_{\text{PI}}(n-1)$$

$$x_{\text{PI}}(n-1)$$

$$x_{\text{PI}}(n-1)$$

$$x_{\text{PI}}(n-1)$$

图1 PI控制器计算框图

Fig.1 Calculation block diagram of PI controller

# 2.2 低通滤波器

在内环控制中,需要对前馈电压进行低通滤波, 本文选取一阶低通滤波器,其传递函数 $G_{LPF}(s)$ 为:

$$G_{\text{LPF}}(s) = \frac{1}{1 + sT_{\text{LPF}}} \tag{3}$$

式中: $T_{LPF}$ 为一阶低通滤波器的时间常数。类似地,采用Tustin变换离散后得到差分方程如下:

$$y_{\text{LPF}}(n) = \frac{T_{\text{S}}}{2T_{\text{LPF}} + T_{\text{S}}} \left( x_{\text{LPF}}(n) + x_{\text{LPF}}(n-1) \right) + \frac{2T_{\text{LPF}} - T_{\text{S}}}{2T_{\text{LPF}} + T_{\text{S}}} y_{\text{LPF}}(n-1)$$

(4)

式中: $x_{LPF}(n)$ 和 $x_{LPF}(n-1)$ 分别为低通滤波器当前时刻和上一时刻的输入信号; $y_{LPF}(n)$ 和 $y_{LPF}(n-1)$ 分别为低通滤波器当前时刻和上一时刻的输出信号。根据式(4)得到低通滤波器的计算框图,如图2所示。低通滤波器的滤波计算同样分为3级:第一级执行1

图2 低通滤波器计算框图

Fig.2 Calculation block diagram of low-pass filter

个加法运算;第二级并行执行2个乘法运算;第三级 执行1个加法运算。

# 2.3 陷波滤波器

在正负序分离环节中,Park变换输出需经过陷波滤波器,以消除2倍频分量[14],选取2阶陷波滤波器,其传递函数 $G_{NF}(s)$ 为:

$$G_{\rm NF}(s) = \frac{s^2 + \omega_{\rm c}^2}{s^2 + 2 \, \xi \omega_{\rm c} s + \omega_{\rm c}^2} \tag{5}$$

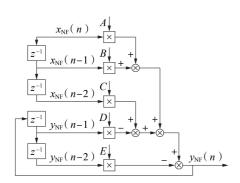

式中: $\omega_c$ =2 $\pi$ ×100 (rad/s)为陷波器特征频率; $\xi$ =0.1为阻尼系数。同样地,将式(5)离散后可以得到式(6)、(7)以及图3所示陷波滤波器的计算框图。

$$y_{NF}(n) = Ax_{NF}(n) + Bx_{NF}(n-1) + Cx_{NF}(n-2) - Dy_{NF}(n-1) - Ey_{NF}(n-2)$$

$$\begin{cases} A = C = \frac{4 + T_{S}^{2} \omega_{c}^{2}}{4 + 4 \xi \omega_{c} T_{S} + T_{S}^{2} \omega_{c}^{2}} \\ B = D = \frac{-8 + 2T_{S}^{2} \omega_{c}^{2}}{4 + 4 \xi \omega_{c} T_{S} + T_{S}^{2} \omega_{c}^{2}} \end{cases}$$

$$E = \frac{4 - 4 \xi \omega_{c} T_{S} + T_{S}^{2} \omega_{c}^{2}}{4 + 4 \xi \omega_{c} T_{S} + T_{S}^{2} \omega_{c}^{2}}$$

$$(7)$$

式中: $x_{NF}(n)$ 、 $x_{NF}(n-1)$  和 $x_{NF}(n-2)$  分别为陷波滤波器当前时刻、前一时刻和前两时刻输入信号; $y_{NF}(n)$ 、 $y_{NF}(n-1)$  和 $y_{NF}(n-2)$  分别为陷波滤波器当前时刻、前一时刻和前两时刻输出信号。图 3 中陷波器的滤波计算分为4级:第一级并行执行5个乘法运算;第二级并行执行1个加法和1个减法运算;第三级执行1个加法运算;第四级执行1个减法运算。

图 3 陷波滤波器计算框图

Fig.3 Calculation block diagram of notch filter

### 2.4 Park 变换及反变换

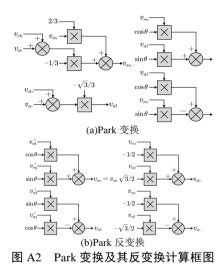

以网侧电压 $v_s$ 为例,说明 Park 变换及其反变换的计算流程。首先通过 Clark 变换将 abc 坐标系变换到  $\alpha\beta$  坐标系,则有:

$$\begin{bmatrix} v_{s\alpha} \\ v_{s\beta} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -1/2 & -1/2 \\ 0 & -\sqrt{3}/2 & -\sqrt{3}/2 \end{bmatrix} \begin{bmatrix} v_{sa} \\ v_{sb} \\ v_{sc} \end{bmatrix}$$

(8)

式中: $v_{sa}$ 、 $v_{sb}$ 和 $v_{sa}$ 、 $v_{sb}$ 、 $v_{sc}$ 分别为 $\alpha\beta$ 坐标系和abc坐标

系下 $v_s$ 的 $\alpha$ 、 $\beta$  轴和a、b、c分量;进一步,将 $\alpha\beta$ 坐标系变换到dq坐标系,如式(9)所示。

$$\begin{bmatrix} v_{sd}^+ \\ v_{sq}^+ \end{bmatrix} = \begin{bmatrix} \cos \theta & \sin \theta \\ -\sin \theta & \cos \theta \end{bmatrix} \begin{bmatrix} v_{s\alpha} \\ v_{s\beta} \end{bmatrix}$$

(9)

式中: $v_{sd}$ 、 $v_{sq}$ 分别为dq坐标系下 $v_s$ 的d、q轴正序分量; cos  $\theta$ 和 sin  $\theta$ 分别为锁相环输出相角 $\theta$ 通过坐标旋转数字计算器 CORDIC (COordinate Rotation DIgital Computer)计算得到的余弦值和正弦值。根据式(8)和式(9)可以得到 Park 变换的计算框图,如附录 A图 A2(a)所示。对式(8)和式(9)求逆可以得到 $\alpha\beta$ 坐标系变换到abc坐标系、dq坐标系变换到 $\alpha\beta$ 坐标系的计算式分别如式(10)、(11)所示。

$$\begin{bmatrix} v_{sa} \\ v_{sb} \\ v_{sc} \end{bmatrix} = \begin{bmatrix} 1 & 0 \\ -1/2 & \sqrt{3}/2 \\ -1/2 & \sqrt{3}/2 \end{bmatrix} \begin{bmatrix} v_{s\alpha} \\ v_{s\beta} \end{bmatrix}$$

(10)

$$\begin{bmatrix} v_{s\alpha} \\ v_{s\beta} \end{bmatrix} = \begin{bmatrix} \cos \theta & -\sin \theta \\ \sin \theta & \cos \theta \end{bmatrix} \begin{bmatrix} v_{sd}^+ \\ v_{sq}^+ \end{bmatrix}$$

(11)

因此,根据式(10)和式(11)可以得到Park 反变换的计算框图,如附录A图A2(b)所示。

类似地,涉及负序分量及环流中2倍频分量的 Park变换和反变换可首先通过三角函数计算得到-θ 和2θ对应的正弦余弦值,并进一步采用附录A图A2 中相同的计算结构得到。

此外,附录A图A1中的有功/无功功率计算环节也可以看作由2级计算组成:第一级并行执行2个乘法运算;第二级执行1个加/减运算。至此,上层控制中所有环节和环流抑制均可由2.1—2.4节内容组合得到。

### 2.5 最近电平调制、电容电压排序和触发信号生成

MMC的直流侧电压依靠分散在各子模块中的电容提供支撑,子模块电容电压均衡是MMC稳定运行的重要前提[15-17]。电容电压排序计算量大,本文选用适合FPGA以及可并行实现的双调排序网络对电容电压排序<sup>[18]</sup>。最近电平调制环节将正负序内环控制和环流抑制输出的调制波整合,并将浮点型变量转换为整型变量,得到各个桥臂需要导通子模块个数。触发信号生成环节根据最近电平调制给出的待导通子模块个数、桥臂电流方向以及电容电压排序结果选择相应子模块投切,生成子模块触发控制信号。

电容电压排序过程中引入保持因子对器件开关 频率进行优化<sup>[19]</sup>。当桥臂电流为充电方向时,将上一时刻导通子模块的电容电压乘以系数  $\lambda_{HFI}(\lambda_{HFI} \leq 1)$ ,上一时刻关断子模块的电容电压乘以系数  $\lambda_{HF2} \leq 1$ );当桥臂电流为放电方向时,将上一时刻导通子模块的电容电压乘以  $\lambda_{HF2}$ ,上一时刻关断子模块的电容电压乘以  $\lambda_{HF1}$ 。经过此预处理后,再将电

容电压输入排序网络进行排序,可以使得已导通(关断)子模块继续优先导通(关断),通过维持原有开关状态不变的方式,降低器件开关频率。

## 2.6 整体时序设计及计算耗时

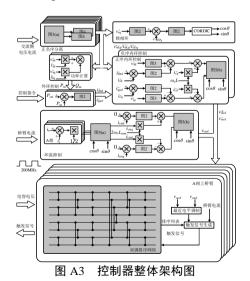

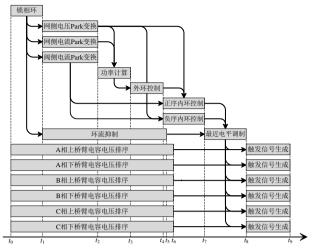

结合 2.1 — 2.5 节内容, 附录 A 图 A3 为本文所开发的 MMC 控制器整体架构图。控制器将 6 个桥臂的均压控制、正/负序内环控制、有功/无功功率计算、三相环流计算以及每种控制中正、负序和 d、q 轴运算均设置为并行执行, 最大限度发挥 FPGA 并行计算特性。

控制器的整体计算时序如附录 A 图 A4 所示。设定所有数据采集完毕后的时刻为起始时刻 t<sub>0</sub>。从 t<sub>0</sub>开始同时进行锁相环计算和 6 个桥臂的电容电压排序。锁相环相角输出后,并行执行网侧电压、电流以及阀侧电流的 Park 变换,得到的结果进一步依次执行功率计算、外环控制、正负序内环控制。其中正序内环控制和负序内环控制结构相同,设置为并行执行。锁相环输出相角还用于 2 倍频环流的 Park 变换,因此环流抑制与交流侧电压、电流的 Park 变换,因此环流抑制与交流侧电压、电流的 Park 变换,因此环流抑制输出结果与正负序内环控制输出结果结合产生调制波,经最近电平调制后得到各个桥臂的待导通子模块个数。最后,根据待导通子模块个数和电容电压的排序结果并行生成各个桥臂中每个子模块的触发信号。

各个环节中,锁相环的计算耗时为 $t_1$ - $t_0$ =222 $T_{\rm elk}$ , Park 变换及正负序分离耗时为 $t_2$ - $t_1$ =91 $T_{\rm elk}$ , 功率计算耗时为 $t_3$ - $t_2$ =19 $T_{\rm elk}$ , 外环控制耗时为 $t_4$ - $t_3$ =61 $T_{\rm elk}$ , 正、负序内环控制耗时为 $t_7$ - $t_4$ =130 $T_{\rm elk}$ , 环流抑制耗时为 $t_5$ - $t_1$ =159 $T_{\rm elk}$ , 最近电平调制耗时为 $t_8$ - $t_7$ =16 $T_{\rm elk}$ 。以单相桥臂包含500个子模块的MMC系统为例,当排序网络并行路数为8时,电容电压排序耗时为 $t_6$ - $t_0$ =482 $T_{\rm elk}$ , 触发信号生成耗时为 $t_9$ - $t_8$ =125 $T_{\rm elk}$ 。综上,整个控制计算耗时为 $t_9$ - $t_0$ =664 $T_{\rm elk}$ 。本文中选用200 MHz的FPGA时钟,即 $T_{\rm elk}$ =5 ns,得到控制计算耗时为3.32  $\mu$ s,而现有控制器实现方案中控制计算耗时约为250  $\mu$ s<sup>[20]</sup>,可见采用本文控制器设计方案可以极大缩短控制计算耗时,对提升系统动态特性有积极作用。

由上述分析可知,对众多子模块电容电压的排序是最为耗时的环节,即使采用并行排序算法,仍旧消耗大量的控制计算时间。增加排序网络路数可以减小排序时间,相应地会增加逻辑计算资源。此外,所开发控制器对于不同电平数 MMC 具有兼容性。当电平数变化时,仅需要根据实际桥臂子模块个数配置排序网络,其余控制环节完全相同。此外,本文基于 FPGA 开发的控制器的优点在于充分发挥了FPGA 的并行计算特性,通过控制模块内并行设计、控制模块间并行处理以及整体时序优化极大提高了

MMC 控制计算速度。此外,本文中所设计控制器集成度高,将所有控制环节在同一芯片内进行,变量均可通过公共寄存资源进行访问,不涉及控制器间的数据传输通信,能够进一步地减小控制器链路延时。

# 3 实验验证

## 3.1 实验系统

为了验证本文所开发控制器的性能,基于RTDS 搭建图 4 所示的单端 201 电平 MMC 系统进行测试,系统的详细参数见附录 A 表 A1。MMC 控制器采用定有功功率和定无功功率控制,整定值分别为  $P_{ref}$  = 200 MW 和  $Q_{ref}$  = 0,控制周期设定为 10  $\mu$ s。

图4 单端201电平MMC测试系统

Fig.4 201-level single-terminal MMC test system

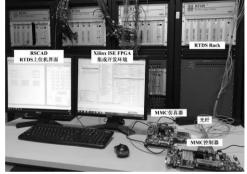

# 3.2 实验平台

附录A图A5为实验平台配置的实物图。本文 使用单块 FPGA 板卡开发实现第2节所述的所有控 制环节,开发环境为Xilinx ISE 14.7,开发语言为 Verilog HDL。开发板为 Xilinx 公司 ML605 集成开 发套件,板上集成了Virtex-6系列FPGA芯片。开发 上述控制器共消耗45%寄存器资源、57%查找表资 源、5% BRAM 资源和 43% DSP481 资源。 MMC 一次 系统运行于RTDS和FPGA组成的仿真器中,FPGA 仿真器用于完成MMC桥臂阀组等值计算和子模块 电容电压更新,RTDS用于完成网络求解[9]。控制器 通过光纤连接 RTDS, 采用 GTFPGA 接口接收 MMC 交流侧电压、电流等运行状态信息和控制指令。控 制器与FPGA 仿真器之间通过6路全双工光纤进行 通信,每路光纤对应1个MMC桥臂。采用传输速率 为2 Gbit / s的开源高速串行 Aurora 协议双向交互子 模块电容电压、桥臂电流和子模块的触发控制字,传 输数据为打包后的数据。

#### 3.3 实验结果

#### 3.3.1 潮流反转

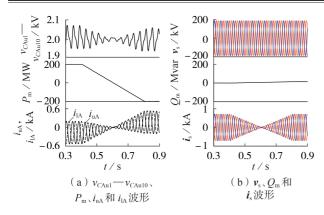

初始状态下,有功功率的整定值  $P_{\text{ref}} = 200 \,\text{MW}$ ,无功功率整定值  $Q_{\text{ref}} = 0$ 。当  $t = 0.4 \,\text{s}$  时,将有功功率整定值调整为  $P_{\text{ref}} = -200 \,\text{MW}$ ,进行潮流反转,有功功率变化率限定为  $2\,000 \,\text{MW}$  / s。图  $5\,$  为潮流反转的实验结果。图中, $v_{CAul}$  一  $v_{CAul0}$  分别为 A 相上桥臂  $SM_1$  一  $SM_{10}$  电容电压; $P_{\text{m}}$ 、 $Q_{\text{m}}$  分别为 MMC 输出的有功、无功功率; $i_{\text{uA}}$  和  $i_{\text{lA}}$  分别为 A 相上、下桥臂电流; $v_{\text{s}}$ 、 $i_{\text{s}}$  分别为网侧交流电压、电流。

由图5可知,有功功率整定值改变后,在控制器 的作用下,有功功率能够准确跟踪整定值,无功功率

### 图 5 潮流反转实验结果

Fig.5 Experimental results of power flow reversal 未受明显扰动。桥臂电流中的直流分量极性发生反转,网侧电流和桥臂电流中的交流分量均经历由大变小再变大的过程,经过约0.2 s的时间平稳过渡到新的稳定运行工作点。

# 3.3.2 开关频率优化

为进一步验证所开发控制器的阀级控制功能,调节保持因子的大小,设定了4种工况进行开关 频率优化实验:工况1为 $\lambda_{HF1}$ =1且 $\lambda_{HF2}$ =1;工况2为 $\lambda_{HF1}$ =0.995且 $\lambda_{HF2}$ =1.005;工况3为 $\lambda_{HF1}$ =0.99且 $\lambda_{HF2}$ =1.01;工况4为 $\lambda_{HF1}$ =0.985且 $\lambda_{HF2}$ =1.015。

选用平均开关频率和电容电压波动率2个指标评价电容电压均衡控制的效果。其中平均开关频率定义为单位时间内单个桥臂所有子模块投切次数(投入和切除各算1次)总和除以桥臂子模块个数的2倍;电容电压波动率定义为电容电压偏离额定值的波动分量幅值与电容电压额定值之比[16]。

初始运行状态同3.3.1节,图6为4种工况下对应的实验结果,图中F<sub>pA</sub>为A相上桥臂SM<sub>1</sub>的触发控制信号。在工况1中,保持因子均为1,相当于未采用开关频率优化的传统均压控制方法。由于每个控制周期都对电容电压排序1次,电容电压的微小变化都会使子模块在最终排序列表中的位置发生变化,造成子模块的反复投切。本文中控制周期仅为10μs,工况1中实测开关频率高达13317 Hz。相应地,工况1中电容电压波动量最小,仅为3.6%。在工况2—4中,随着保持因子的调整,开关频率优化程度逐渐加深,开关频率由工况2中的227 Hz下降到工况4中的146 Hz,电容电压波动率由3.9%升高到4.05%。可见通过合理选择保持因子大小可以在不显著牺牲子模块电容电压均压效果的情况下,有效降低开关频率,进而减小器件的开关损耗。

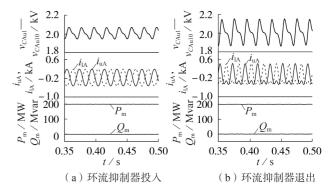

#### 3.3.3 环流抑制器投退

初始状态同上,图7(a)和图7(b)分别为环流抑制器投入和退出时的实验波形。环流是在换流器内

图 6 开关频率优化实验结果

Fig.6 Experimental results of switching

frequency optimization

图7 环流抑制器投退实验结果

Fig.7 Experimental results of circulating current suppressor in and out of service

部流动的2倍频分量,从图7中可以看到,当环流抑制器投入时,桥臂电流中的2倍频分量能够得到有效抑制。由于桥臂电流直接对子模块电容进行充放电,这也减小了子模块电容电压的波动幅度。此外,对比图7(a)和图7(b),环流抑制器的投退对上层控制的影响很小,图7中有功功率和无功功率均能准确跟踪整定值。

综合以上3种模式下的实验结果可知,本文开 发的控制器均能够取得良好的控制效果。

#### 4 结论

本文基于FPGA设计了一种MMC控制器,进行了硬件在环实验对控制器性能进行验证,得到如下

### 结论:

- 1)所设计的控制器具有较高的集成度,能灵活实现不同的调制和控制策略,在单块FPGA板卡中即可实现MMC的所有控制环节;

- 2)通过将控制环节集成并行化设计,能够大幅减少因控制计算、数据通信导致的链路延时,本文中对于501电平系统,控制计算耗时仅为3.32 μs;

- 3)通过潮流反转、开关频率优化、环流抑制器投退实验验证了所设计的控制器的功能,控制器可用于一次参数设计论证、控制参数优化、控制策略验证等领域。

附录见本刊网络版(http://www.epae.cn)。

# 参考文献:

- [1] 茆书睿,徐政,杨健,等.交流系统短路故障下MMC对短路 电流的影响及抑制策略[J]. 电力自动化设备,2020,40(12): 134-142

- MAO Shurui, XU Zheng, YANG Jian, et al. Influence analysis and control strategy of MMC on AC short circuit current under short circuit fault of AC system[J]. Electric Power Automation Equipment, 2020, 40(12):134-142.

- [2] 孙吉波,王宇,刘崇茹,等. 基于MMC的多端直流电网双极短路故障电流计算[J]. 电力自动化设备,2018,38(11):72-78. SUN Jibo, WANG Yu, LIU Chongru, et al. Pole-to-pole short circuit current calculation of multi-terminal DC grid based on MMC[J]. Electric Power Automation Equipment, 2018, 38 (11):72-78.

- [3] 汤广福,庞辉,贺之渊. 先进交直流输电技术在中国的发展与应用[J]. 中国电机工程学报,2016,36(7):1760-1771.

TANG Guangfu, PANG Hui, HE Zhiyuan. R&D and application of advanced power transmission technology in China[J]. Proceedings of the CSEE,2016,36(7):1760-1771.

- [4] WANG C Y, XIAO L, JIANG H J, et al. Analysis and compensation of the system time delay in an MMC system[J]. IEEE Transactions on Power Electronics, 2018, 33(11):9923-9936.

- [5] 邹常跃,陈俊,许树楷,等. 长控制链路延时特征下柔性直流输电系统动态性能改善方法[J]. 电网技术,2017,41(10):3216-3222.

- ZOU Changyue, CHEN Jun, XU Shukai, et al. Dynamic performance optimization of VSC-HVDC considering its long delay [J]. Power System Technology, 2017, 41(10):3216-3222.

- [6] 黄林彬,辛焕海,鞠平,等. 电力电子并网装备的同步稳定分析与统一同步控制结构[J]. 电力自动化设备,2020,40(9):10-25. HUANG Linbin, XIN Huanhai, JU Ping, et al. Synchronization stability analysis and unified synchronization control structure of grid-connected power electronic devices[J]. Electric Power Automation Equipment,2020,40(9):10-25.

- [7] 徐文波,田耘. Xilinx FPGA开发实用教程[M]. 2版. 北京:清 华大学出版社,2012;8-18.

- [8] 沈卓轩,姜齐荣. 电力系统电磁暂态仿真IGBT详细建模及应用[J]. 电力系统自动化,2020,44(2):234-246.

SHEN Zhuoxuan,JIANG Qirong. Detailed IGBT modeling and applications of electromagnetic transient simulation in power system[J]. Automation of Electric Power Systems,2020,44(2):

- [9] 王宇,刘崇茹,李庚银. 基于FPGA的模块化多电平换流器实

- 时仿真建模与硬件在环实验[J]. 中国电机工程学报,2018,38 (13):3912-3920,4033.

- WANG Yu, LIU Chongru, LI Gengyin. FPGA-based real-time modeling of modular multilevel converters and hardware-in-the-loop simulation[J]. Proceedings of the CSEE, 2018, 38(13): 3912-3920, 4033.

- [10] 王宇,刘崇茹,凌博文,等. 集成排序网络的模块化多电平换流器实时仿真模型[J]. 电网技术,2020,44(3):1090-1098. WANG Yu,LIU Chongru,LING Bowen, et al. Real-time simulation model of modular multilevel converter with sorting network integrated [J]. Power System Technology, 2020, 44(3): 1090-1098.

- [11] 张迪,辛业春,李国庆,等. 基于RT-LAB的模块化多电平换流器半实物仿真平台设计[J]. 现代电力,2019,36(4):57-64. ZHANG Di, XIN Yechun, LI Guoqing, et al. Design of hardware in the loop simulation platform for MMC based on RT-LAB[J]. Modern Electric Power,2019,36(4):57-64.

- [12] 田鹏飞,刘崇茹,洪国巍,等. 模块化多电平换流器半实物仿 真平台设计与实验验证[J]. 电力系统自动化,2016,40(1): 122-128.

- TIAN Pengfei, LIU Chongru, HONG Guowei, et al. Design and experimental verification of a hardware-in-the-loop simulation platform for modularized multilevel converter [J]. Automation of Electric Power Systems, 2016, 40(1):122-128.

- [13] YEPES A G, FREIJEDO F D, DOVAL-GANDOY J, et al. Effects of discretization methods on the performance of resonant controllers [J]. IEEE Transactions on Power Electronics, 2010,25(7):1692-1712.

- [14] AJI H, NDREKO M, POPOV M, et al. Investigation on different negative sequence current control options for MMC-HVDC during single line to ground AC faults [C]//2016 IEEE PES Innovative Smart Grid Technologies Conference. Ljubljana, Slovenia; IEEE, 2016; 1-6.

- [15] LI W, GRÉGOIRE L A, BÉLANGER J. A modular multilevel converter pulse generation and capacitor voltage balance method optimized for FPGA implementation[J]. IEEE Transactions on Industrial Electronics, 2015, 62(5);2859-2867.

- [16] 王宇,刘崇茹,李庚银,等. 适用于FPGA的模块化多电平换流器电容电压均衡控制方法[J]. 电力系统自动化,2019,43(8):167-173.

- WANG Yu, LIU Chongru, LI Gengyin, et al. Capacitor voltage balancing control method for modular multilevel converter applicable for FPGA[J]. Automation of Electric Power Systems, 2019,43(8):167-173.

- [17] 屠卿瑞,徐政,郑翔,等. 一种优化的模块化多电平换流器电压 均衡控制方法[J]. 电工技术学报,2011,26(5):15-20. TU Qingrui,XU Zheng,ZHENG Xiang,et al. An optimized voltage balancing method for modular multilevel converter[J]. Transactions of China Electrotechnical Society, 2011, 26(5): 15-20.

- [18] 顾乃杰,王旭,陈国良,等. 并行双调排序算法的有效实现及性能分析[J]. 计算机研究与发展,2002,39(10):1343-1348. GU Naijie,WANG Xu,CHEN Guoliang,et al. An efficient implementation and performance analysis of parallel bitonic sorting[J]. Journal of Computer Research and Development,2002, 39(10):1343-1348.

- [19] 管敏渊,徐政. MMC型 VSC-HVDC 系统电容电压的优化平衡控制[J]. 中国电机工程学报,2011,31(12):9-14.

GUAN Minyuan,XU Zheng. Optimized capacitor voltage balancing control for modular multilevel converter based VSC-HVDC system[J]. Proceedings of the CSEE,2011,31(12):9-14.

- [20] ZOU C Y, RAO H, XU S K, et al. Analysis of resonance

between a VSC-HVDC converter and the AC grid[J]. IEEE Transactions on Power Electronics, 2018, 33(12):10157-10168.

#### 作者简介:

王 宇(1993—),男,辽宁营口人,博士研究生,主要研究方向为柔性直流输电系统控制策略(E-mail:wangyu\_ncepu@163.com):

刘崇茹(1977一),女,陕西西安人,教授,博士,主要从

事交直流混合系统分析与仿真、运行与控制方面的科研和教学工作(E-mail:chongru.liu@ncepu.edu.cn);

候延琦(1995—),男,吉林白城人,博士研究生,主要研究方向为柔性直流输电系统实时仿真建模( $\mathbf{E}$ -mail:houyanqi@ncepu.edu.cn)。

王宇

(编辑 王欣竹)

# Parallel controller design and experimental verification for modular multilevel converter based on FPGA

WANG Yu,LIU Chongru,HOU Yanqi,LIU Haoyu,LI Gengyin (State Key Laboratory of Alternate Electrical Power System with Renewable Energy Sources,

North China Electric Power University,Beijing 102206,China)

Abstract: The thousands of sub-modules in MMC (Modular Multilevel Converter) bring a great calculation burden to the controller. Massive data acquisition, complex control calculation and communication between different controllers lead to long control link delay, which further deteriorates the dynamic characteristics of the system and even leads to instability of the system after grid connection. An integrated controller based on FPGA (Field Programmable Gate Array) is designed to implement all the control strategies of MMC in a single FPGA board. The controller makes full use of the parallel characteristics of FPGA. Each control block is designed in parallel as much as possible, and the independent control blocks are executed in parallel to improve the calculative speed of the controller. Based on the RTDS platform, hardware-in-the-loop experiments are carried out to verify the function of the developed controller. The results show that the controller has short link delay and fast response speed, which can be used in the development test of control strategies, control parameter debug and other fields.

**Key words:** modular multilevel converter; controller; field programmable gate array; parallel calculation; hardware-in-the-loop

(上接第81页 continued from page 81)

# Suppression method of inverter common-mode voltage based on virtual space vector over-modulation strategy

WANG Shun, YANG Shuying, LI Yi, XIE Zhen

(School of Electrical Engineering and Automation, Hefei University of Technology, Hefei 230009, China)

Abstract: VSVM (Virtual Space Vector Modulation) technology has received wide attentions for its distinct merits in CMV (Common-Mode Voltage) suppression. Compared with SVPWM (Space Vector Pulse Width Modulation) strategy, the allowable linear modulation range of VSVM strategy is reduced, which affects the output voltage of the inverter. The CMV characteristics and the linear modulation range with and without zero-vector modulation strategy are analyzed. On this basis, an over-modulation strategy for VSVM strategy is proposed, and the mathematical relationship between the over-modulation compensation angles and the modulation ratios is deduced, and the implementation process of the proposed strategy is designed. Finally, the inverter CMV characteristics and the linear modulation range with the proposed strategy are analyzed by the experiments. The experimental results verify the correctness of theoretical analysis and the feasibility of the proposed strategy.

**Key words:** virtual space vector modulation; common-mode voltage; over-modulation; modulation range; electric inverters

# 附录 A

图 A1 MMC 结构及控制原理

Fig.A1 Structure and control principle of MMC

Fig.A2 Calculation block diagram of Park transformation and inverse Park transformation

Fig.A3 Diagram of controller overall architecture

图 A4 控制器计算时序图

Fig. A4 Controller calculation sequence diagram 表 A1 实验系统参数

Table A1 Parameters of experimental system

| 对象   | 参数                          | 数值         |

|------|-----------------------------|------------|

| 交流系统 | 交流系统电压 $V_{\rm SN}/{ m kV}$ | 230        |

|      | 交流系统等值阻抗 $Z_{\rm S}/\Omega$ | 0.1+j0.314 |

| 变压器  | 变压器额定容量 $S_N/(MV A)$        | 500        |

|      | 变压器变比 k                     | 230/225    |

|      | 变压器漏抗 $X_T$                 | 0.1        |

| ММС  | 子模块电容 $C_{SM}/mF$           | 6.6        |

|      | 桥臂串联电抗 $L_{arm}/mH$         | 50         |

|      | 桥臂子模块个数 N                   | 200        |

| 直流系统 | 直流电压 V <sub>DC</sub> /kV    | ±200       |

|      | 直流线路电阻 $R_{DC}/\Omega$      | 1.0        |

|      | 直流线路电感 $L_{DC}/H$           | 0.1        |

|      |                             |            |

注:  $X_T$  为标幺值。

图 A5 硬件在环实验平台配置

Fig.A5 Configuration of hardware-in-loop experimental platform