# 基于滤波器前置的三相软件锁相环设计

刘启德1,王海云1,王浩成2,徐 永1

(1. 新疆大学 电气工程学院 教育部可再生能源发电与并网控制工程技术研究中心,新疆 乌鲁木齐 830047; 2. 伊犁师范大学 电子与信息工程学院,新疆 伊宁 835000)

摘要:针对传统锁相环在电压不平衡及畸变时锁相误差大、动态响应速度慢的问题,根据软件锁相环(SPLL)的原理提出一种滑动滤波器(MAF)前置锁相环,并通过一种快速不平衡分量抑制及相位延迟补偿的方法来改善MAF性能,有效提高了锁相环的动态响应速度和锁相精度。通过MATLAB/Simulink仿真平台及TMS320F28335数字信号处理器芯片对所提出的锁相环控制策略在三相电压不平衡及电压畸变的条件下进行验证,结果表明该SPLL锁相误差小,动态响应速度快,稳定性高。

关键词:软件锁相环;滑动滤波器;相位延时补偿;电压畸变;数字信号处理器

中图分类号:TN 713;TN 850.4

文献标志码:A

DOI: 10.16081/j.epae.202104010

# 0 引言

传统锁相环基于单同步坐标系变换原理,通过 PI 控制实现三相软件锁相环 SPLL(Software Phase Locked Loop),但是当电压含有谐波或发生不平衡 故障时,传统锁相环存在锁相误差大、动态响应时间 长(大于1个工频周期)的问题[1]。

文献[2]通过降低锁相环控制环路带宽可以有 效抑制电网中的谐波电压,但是当电网发生单相接 地故障时锁相误差大。文献[3]提出一种基于双同 步坐标系解耦的锁相环(DDSRF-PLL),采用正、负序 的双同步坐标系结构和解耦的方式消除正、负序间 的耦合关系,提取出正序分量,有效解决了三相不对 称时的锁相问题,但是其结构复杂,当电网中含有谐 波时,动态响应时间长,无法满足高性能锁相环对快 速性的要求。为了增强锁相环的滤波能力,在传统 SPLL结构的基础上,文献[4]提出一种基于自适应 陷波器的锁相环(ANF-PLL),有效抑制了不对称电 压在 dq 轴上产生的 2 倍频分量。文献 [5] 提出通过 在控制环路内并联多台陷波器以消除电网中特定次 的谐波,在实际设计中,必然要在陷波器的数量和程 序运行时间间进行权衡。文献[6-7]根据交叉解耦 双复系数滤波器(DCCF)在零频率附近具有不对称 的频率响应的特性,提取和分离电压正、负序分量, 在电网发生不对称故障及含有谐波或频率发生偏移 时均有较好的锁相精度,但是其响应时间约为2个 工频周期。文献[8-9]提出一种基于延时信号消除 不平衡分量及谐波的方法,可以针对不同电网工况

收稿日期:2020-07-27:修回日期:2021-01-29

基金项目:自治区重点研发计划(2020B02001);自治区高校重大项目(XJEDU2017I002)

Project supported by the Key Research and Development Plan of Autonomous Region(2020B02001) and the Major Projects of Universities in Autonomous Region(XJEDU2017I002) 对延时消除环节进行快速设计,然而当电网中谐波成分越复杂时,其级联的延时模块也越多。相比于陷波器及信号延时滤波的方法,滑动滤波器 MAF (Moving Average Filter)以其完全抑制某些特定频率而不需要级联或并联的幅频特性在锁相环中得到广泛使用。文献[10-11]将 MAF 置于锁相环控制环路之内,有效抑制了电网中的不平衡分量及谐波,但降低了锁相环的响应速度及相角裕度。文献[12]提出将 MAF 置于锁相环控制环路之外,提高了锁相环的环路带宽,但是额外需要一个频率检测装置,增加了算法的复杂度。

本文提出一种基于MAF的滤波器前置SPLL,针对MAF动态响应时间长及频率适应差的问题,采用一种快速消除2倍频负序分量的方法来降低MAF的阶数,提高锁相环的动态响应速度,同时采用线性相位补偿的方式来减小MAF在电网频率发生偏移时产生的锁相误差。仿真及实验结果验证了所提锁相环性能良好。

#### 1 SPLL

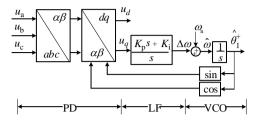

SPLL主要由鉴相器 PD(Phase Detector)、环路滤波器 LF(Loop Filter)、压控振荡器 VCO(Voltage-Controlled Oscillator)三部分组成。三相输入电压  $u_a$ 、 $u_b$ 、 $u_c$ 经过 Park 变换转换到与三相电压同步旋转的 dq 坐标系,得到交流电压的 d、q 轴分量( $u_a$ 、 $u_q$ ),在进行 Park 变换时所使用的相位角是 SPLL输出的相位角  $\hat{\theta}_1^*$ ,当电网相位与锁相环相位不相等时, $u_q$ 在 PI 控制器的调节下趋于给定值 0,从而达到锁定相位的目的。传统 SPLL的结构框图见附录中图  $\mathbf{A}1^{[13]}$ 。

# 1.1 电网电压模型

在电网电压理想的情况下,传统SPLL可以精确锁相,但是当电网由于故障导致三相电压严重不对称时,传统SPLL就难以满足高性能锁相环对快速性

125

及准确性的要求。因此准确建立电网电压模型是锁相环设计的基础。

由对称分量法可知电网三相电压可分解为正序、负序和零序3组对称电压分量。由于零序电压经过Clark变换后为0,对结果没有影响,不做考虑。则电网电压可表示为:

$$\begin{cases} u_{a}(t) = \sum_{h=1}^{+\infty} \left[ U_{h}^{+} \cos (h\omega t + \theta_{h}^{+}) + U_{h}^{-} \cos (h\omega t + \theta_{h}^{-}) \right] \\ u_{b}(t) = \sum_{h=1}^{+\infty} \left[ U_{h}^{+} \cos \left( h\omega t + \theta_{h}^{+} - \frac{2\pi}{3} \right) + U_{h}^{-} \cos \left( h\omega t + \theta_{h}^{-} + \frac{2\pi}{3} \right) \right] \\ u_{c}(t) = \sum_{h=1}^{+\infty} \left[ U_{h}^{+} \cos \left( h\omega t + \theta_{h}^{+} + \frac{2\pi}{3} \right) + U_{h}^{-} \cos \left( h\omega t + \theta_{h}^{-} - \frac{2\pi}{3} \right) \right] \end{cases}$$

$$(1)$$

其中, $\omega$ 为电网电压基波角频率; $U_h^+$ 、 $U_h^-$ 和  $\theta_h^+$ 、 $\theta_h^-$ 分别为三相电压中h倍频正序、负序分量的幅值和相位,三相电压主要含 5、11、···· 倍频负序分量和 7、13、···· 倍频正序分量 [14]。

对三相电压进行等量 Park 变换且基于旋转坐标系 q 轴锁定时,即  $\omega = \hat{\omega}$ ,  $\theta_1^+ \approx \hat{\theta}_1^+$ , 通过泰勒公式可知当  $\Delta x \approx 0$  时, $\sin \Delta x \approx \Delta x$ ,  $\cos \Delta x \approx 1$ , 可得到同步旋转坐标系下电网电压表达式为:

$$\begin{bmatrix} u_{d}(t) \\ u_{q}(t) \end{bmatrix} \approx \begin{bmatrix} U_{1}^{+} \\ U_{1}^{+}(\theta_{1}^{+} - \hat{\theta}_{1}^{+}) \end{bmatrix} + \begin{bmatrix} \sum_{h=2}^{+\infty} U_{h}^{+} \cos X + \sum_{h=1}^{+\infty} U_{h}^{-} \cos Y \\ \sum_{h=2}^{+\infty} U_{h}^{+} \sin X + \sum_{h=1}^{+\infty} U_{h}^{-} \sin Y \end{bmatrix}$$

$$\begin{cases} X = (h-1)\omega t + \theta_{h}^{+} - \hat{\theta}_{1}^{+} \\ Y = (h+1)\omega t + \theta_{h}^{-} + \hat{\theta}_{1}^{+} \end{cases}$$

(2)

式(2)的约等于号右侧第一项近似为常数项;第二项主要为基频不对称分量所产生的2倍频分量以及5、11、…倍频负序分量和7、13、…倍频正序分量占主导的非3次谐波所产生的6、12、…倍频分量。1.2 滤波器前置SPLL

由于传统锁相环在电网发生不平衡故障及电网畸变时无法滤除式(2)中约等于号右侧第二部分产生的干扰,近几年提出的新型锁相环也主要基于传统 SPLL 的结构加入各种形式的滤波器来增强锁相环的滤波能力<sup>[15-16]</sup>。按照滤波器在锁相环中的位置,可将锁相环分为环内滤波器 SPLL和滤波器前置 SPLL。为了分析两者的性能,给出其小信号模型如图 1 所示。图中,θ为电网电压的实际相位;ω<sub>n</sub>为电网额定角频率。

由小信号模型可以得出环内滤波器 SPLL 和滤波器 SPLL 的开环传递函数分别见式(3)和式(4)。

$$\begin{array}{c} \theta_{c} & \theta_{c} & \theta_{c} \\ + & \delta_{c} & \delta_{c} \\ \end{array}$$

(a) 坏闪滤波器 SPLL

(b)滤波器前置 SPLL

#### 图1 SPLL的s域小信号模型

Fig.1 Small-signal model of SPLL in s-domain

$$G_{\text{ol}}(s) = \frac{\hat{\theta}_1^+}{\theta} = G_{\text{MAF}}(s)L(s)\frac{1}{s}$$

(3)

$$G_{\text{ol}}^{\text{p}}(s) = \frac{\hat{\theta}_{1}^{+}}{\theta_{s}} = L(s) \frac{1}{s} \tag{4}$$

其中, $G_{ol}(s)$ 、 $G_{ol}^{P}(s)$ 分别为环内滤波器 SPLL 和滤波器 前置 SPLL 的传递函数;L(s)、 $G_{MAF}(s)$ 分别为环路滤波器和 MAF 的传递函数; $\theta_{e}$ 为锁相误差,是 SPLL 输出相位  $\hat{\theta}_{1}^{e}$ 与电网相位  $\theta_{1}^{e}$ 的差值。

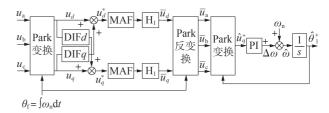

MAF的传递函数可近似为一阶低通滤波器,对比式(3)和式(4)可以看出环内滤波器 SPLL会降低环路带宽,减小系统相角裕度<sup>[15,17]</sup>,且增加了环路滤波器参数设计的复杂性。本文提出一种滤波器前置 SPLL来提高锁相环的动态响应速度。滤波器前置 SPLL的结构框图如图 2 所示。

图 2 滤波器前置 SPLL 的结构框图

Fig.2 Schematic diagram of SPLL based on prefilter

电网三相电压在以 $\theta_{\rm f} = \int \omega_{\rm n} {

m d}t (\theta_{\rm f})$  的初始相位可以为任意值,对本文所提锁相环算法的结果没有影响)为相位的旋转坐标系下经过 Park 变换得到  $u_d$ 、 $u_q$ 。通过在 MAF 前加入负序分量抑制算法来消除式(2)中约等于号右侧的 2 倍频负序分量以减小 MAF 阶数,提高锁相环响应速度,并对信号经过 MAF 产生的线性相移进行补偿,以准确地获得电网电压的正序分量  $\bar{u}_d$ 、 $\bar{u}_q$ ,然后由 Park 反变换得到只包含电网正序分量的三相电压  $\bar{u}_a$ 、 $\bar{u}_b$ 、 $\bar{u}_e$ ,再由 Park 变换获得包含电网相位信息的直流分量  $\hat{u}_q^*$ ,并通过 PI 控制快速锁定电网相位。

# 2 滤波器前置 SPLL 的设计方法

滤波器前置 SPLL 以 MAF 为基础, MAF 具有结构简单、幅频特性优异、运算时间较少等优点[18], 但

存在响应速度慢、频率自适应差、相移等问题[11.19], 所以在进行滤波器前置 SPLL 的设计时主要针对 MAF的缺点对其进行改进。

#### 2.1 微分模块的设计

微分(DIF)模块通过对 $u_a$ 、 $u_q$ 进行微分的方式快速消除其包含的2倍频负序分量。DIF子模块DIFd、DIFq的传递函数分别为:

$$G_{\text{DIE}_d}(s) = -s/(2\omega_{\text{n}}) \tag{5}$$

$$G_{\text{DIF}_a}(s) = s/(2\omega_n) \tag{6}$$

根据图2,联立式(2)、(5)和(6)可得:

$$\begin{bmatrix} u_{d}^{*} \\ u_{q}^{*} \end{bmatrix} = \begin{bmatrix} u_{d} + u_{q} G_{\text{DIF}q} \\ u_{q} + u_{d} G_{\text{DIF}d} \end{bmatrix} = \begin{bmatrix} u_{d} + \frac{u_{q}'}{2\omega_{n}} \\ u_{q} - \frac{u_{d}'}{2\omega_{n}} \end{bmatrix} = \begin{bmatrix} U_{1}^{+} \\ U_{1}^{+} (\theta_{1}^{+} - \hat{\theta}_{1}^{+}) \end{bmatrix} + \\ \sum_{h = 7, 13, \dots} \frac{h+1}{2} U_{h}^{+} \begin{bmatrix} \cos \left[ (h-1)\omega t + \theta_{h}^{+} - \hat{\theta}_{1}^{+} \right] \\ \sin \left[ (h-1)\omega t + \theta_{h}^{+} - \hat{\theta}_{1}^{+} \right] \end{bmatrix} + \\ \sum_{h = -5, -11, \dots} \frac{h+1}{2} U_{h}^{-} \begin{bmatrix} \cos \left[ (h-1)\omega t + \theta_{h}^{-} - \hat{\theta}_{1}^{+} \right] \\ \sin \left[ (h-1)\omega t + \theta_{h}^{-} - \hat{\theta}_{1}^{+} \right] \end{bmatrix}$$

(7)

其中, $u_a^*$ 、 $u_q^*$ 分别为 $u_a$ 、 $u_q$ 消除2倍频负序分量后的直流分量; $u_a'$ 、 $u_a'$ 分别为 $u_a$ 、 $u_a$ 的微分形式。

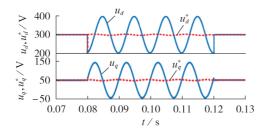

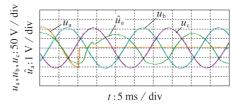

由式(7)可见,DIF模块可以消除电网中的基波负序分量,但会增大其他谐波的幅值,而 MAF 将对这些谐波进行有效抑制。当电网电压基波角频率  $\omega=\omega_n=314 \text{ rad/s}$ 时,基频正序分量  $U_1^+=311 \text{ V}$ , $\theta_1^+$  初始相位为  $110^\circ$ ,基频负序分量  $U_1^-=100 \text{ V}$ , $\theta_1^-$  初始相位为  $10^\circ$ ,相位角  $\theta_1$  初始相位为  $0^\circ$  时, $u_a$ 、 $u_q$  中的不平衡分量经过 Park 变换后被 DIF模块消除,如图 3 所示。

图3 不平衡分量经过DIF模块的波形

Fig.3 Waveforms of unbalanced components passing through DIF module

# 2.2 MAF的设计

MAF是一种具有线性相位的有限脉冲响应滤波器,在特定情况下其特性和一个理想的低通滤波器相近,设MAF的输入信号为x(t),输出信号为 $\bar{x}(t)$ ,则其传递函数为:

$$G_{\text{MAF}}(s) = \frac{\bar{x}(t)}{x(t)} = \frac{1 - e^{-T_{\omega}s}}{T_{\omega}s}$$

(8)

其中, $T_{\omega}$ 为 MAF 的采样时间窗长度。将  $s = j\omega$  代人式(8)可得 MAF 的幅频及相频表达式为:

$$G_{\text{MAF}}(j\omega) = \left| \frac{\sin(\omega T_{\omega}/2)}{\omega T_{\omega}/2} \right| \angle -\omega T_{\omega}/2 \tag{9}$$

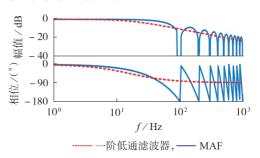

从式(8)可以看出,MAF到达稳态的时间等于 $T_{\omega}$ ,  $T_{\omega}$  越大则 MAF的瞬时响应速度越慢,因此选择一个合适的  $T_{\omega}$  对锁相环而言非常重要。从式(9)可以看出 MAF 在输入信号频率  $f_i$ =0时增益为1,当输入信号频率  $f_i$ = $n/T_{\omega}$  (n=1,2,…)时增益为0。这说明 MAF可以滤除  $n/T_{\omega}$  的信号。当  $T_{\omega}$ =0.01 s时 MAF和截止频率为100 Hz的一阶低通滤波器的幅频、相频响应对比图如图4所示。

图4 MAF及一阶低通滤波器的波特图

Fig.4 Bode diagram of MAF and first order LPF

$T_{\omega}$ 是MAF设计中最重要的一个参数,对 $T_{\omega}$ 进行设置时必须在MAF的动态响应速度和滤波能力之间进行权衡。通常以滤除电网中所包含的最低次主要谐波频率作为 $T_{\omega}$ 的选择原则。文献[15]为了消除不平衡电网电压产生的基波负序分量,将 $T_{\omega}$ 设置为电网基频周期T的一半即T/2,这虽然增强了MAF的滤波能力,但降低了其动态响应速度。对比式(2)和式(7)可看出,本文所提 SPLL通过 DIF 模块抑制电网中的基波负序分量,可将电网中最低次主要谐波频率提高至基频的 6倍,所以本文设计 MAF 时将 $T_{\omega}$ 设置为T/6,在满足对电网电压采样信号中最低次主要谐波抑制的同时,提高 SPLL的动态响应速度。

#### 2.3 MAF相位延时补偿

根据图 2,当三相电压信号以额定角频率经过 Park 变换时,在旋转坐标系下式(2)中约等于号右侧第一项为常数。但是电网频率不是静止不变的,在正常情况下,根据国际电工委员会标准 IEC 61000-2-2,电网频率偏移应不超过  $\pm 1$  Hz。当频率发生偏移时,式(2)中约等于号右侧第一项为低频振荡分量,由式(9)可知低频振荡分量经过 MAF将产生时间延迟,从而产生锁相误差。时间延迟  $t_4$ 为:

$$t_{\rm d} = N/(2f_{\rm s}) \tag{10}$$

其中, $N = T_{\omega} / f_s$ 为 MAF 阶数, $f_s$ 为采样频率。为了消除锁相误差,必须对经过 MAF 的信号 $u_d$ 、 $u_q$ 进行延时补偿。由式(10)可知, $t_d \ll 2\pi / \omega_d$ ,其中 $\omega_d$ 为角频率偏移,可以认为在任何 $t_d$ 的时间段内, $u_d$ 、 $u_q$ 都是线性变化的<sup>[19]</sup>。因此可以通过当前采样时刻的值来预测下一时刻的采样值,用数学公式可以表达为:

$$y(k+1) = y(k) + m/f_s$$

(11)

其中,y(k),y(k+1)分别为当前时刻和下一时刻的采样值;m为斜率。令 $N_1$ 为 $t_d$ 内的采样个数,则 $N_1$ 为:

$$N_1 = t_{\rm d} f_{\rm s} = N/2 \tag{12}$$

据此可以通过 $N_1$ 来利用当前 $t_a$ 内的输出值去预测下一 $t_a$ 内的输出值,联立式(11)和式(12)可得相位延时补偿模块 $H_1$ 在离散域的传递函数 $H_1(z)$ 为:

$$H_1(z) = (N_1 + 1) - N_1 z^{-1}$$

(13)

根据 MAF本身的结构,可以对 H<sub>1</sub>进一步优化得到<sup>[18]</sup>:

$$H_{1}(z) = \frac{(N_{1} + 1) - (N_{1} - \varepsilon)z^{-1}}{1 + \varepsilon}$$

(14)

其中, $\varepsilon$ 为优化因子,且 $\varepsilon \ll 1$ 。

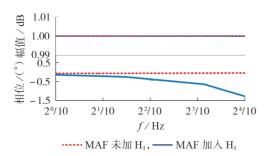

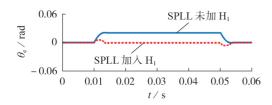

当  $T_{\omega}$ = 0.003 3 s,  $f_s$ = 10 kHz,  $\varepsilon$ = 0.009 5 时, MAF 有无 H<sub>1</sub>时的低频段波特图如图 5 所示。可以看出,H<sub>1</sub>可以补偿低频信号经过 MAF 时所产生的相移,因为对于低频信号 H<sub>1</sub>会产生一个线性的正向相移,以补偿 MAF 产生的线性的负向相移<sup>[19]</sup>。

图 5 MAF 有无 H, 时的低频段波特图

Fig. 5 Bode diagram of MAF with and without  $H_1$  at low frequency

当电网角频率 $\omega$ =314 rad / s,基频正序分量  $U_1^+$ =311 V, $\theta_1^+$ 初始相位为 10°, $\theta_1^-$ 初始相位为 0°时,在0.01 s时频率发生 2 Hz偏移并在 0.05 s时恢复,滤波器前置 SPLL输出相位与电网相位的差值如图 6 所示。

图 6 频率偏移 2 Hz 时滤波器前置 SPLL 有无 H, 时的相位误差

Fig.6 Phase error of SPLL based on prefilter with and without H<sub>1</sub> when frequency offset is 2 Hz

# 3 仿真对比

为了评估本文所提SPLL的性能,基于MATLAB/ Simulink仿真平台,在仿真环境为10 kHz的定步长 离散解算器下搭建SPLL模型,并与在工程中应用 最广泛的基于同步坐标系的锁相环(SRF-PLL)及基 于滑动滤波器的锁相环(MAF-PLL)进行对比。初始输入电压为不含谐波的三相平衡电压,其幅值为311 V、额定频率为50 Hz、初始相位为10°,θ<sub>Γ</sub>的初始相位为0°,仿真时所设定的电网情况见表1。

#### 表1 不同仿真案例所设定的电网情况

Table 1 Grid conditions set by different simulation cases

| 案例 | 设定条件                                                                                                                                             |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | 在0.08 s时电网频率发生2 Hz跳变并在0.12 s时恢复                                                                                                                  |

| 2  | 在0.08 s时电网相位发生-40°跳变并在0.12 s时恢复                                                                                                                  |

| 3  | 在0.08 s时电网a相电压跌落至0并在0.12 s时恢复                                                                                                                    |

| 4  | 在 $0.08~\mathrm{s}$ 时电网相位跳变 – $20^\circ$ 并向电网中注入 $10\%$ 的 – $5\%$ 、 $5\%$ 的 $7\%$ 、 $5\%$ 的 – $11\%$ 、 $2\%$ 的 $13次谐波$ ,并在 $0.12~\mathrm{s}$ 时恢复 |

| 5  | 在 0.08 s 时刻电 网角 频率以 3.49 rad / s 的速度发生偏移,<br>且向电 网中注入 10% 的 -5 次、5%的 7 次、5%的 -11 次、<br>2%的 13 次 谐波 并在 0.12 s 时恢复                                 |

SRF-PLL和MAF-PLL的PI控制器参数设计方法分别参照文献[2]和[15](本文所提SPLL的PI控制器参数设计方法同SRF-PLL),具体参数见表2。表中, $K_p$ 、 $K_i$ 分别为PI控制器的比例和积分系数; $f_c$ 为截止频率; $P_M$ 为相角裕度。

表 2 所提 SPLL、SRF-PLL、MAF-PLL的仿真参数

Table 2 Simulation parameters of proposed SPLL,

SRF-PLL and MAF-PLL

| 锁相环     | 参数                                                                      | 开环传递函数特性                                                          |

|---------|-------------------------------------------------------------------------|-------------------------------------------------------------------|

| 所提SPLL  | $K_{\rm p} = 13.4, K_{\rm i} = 23263,$<br>$T_{\rm o} = 0.003 \text{ s}$ | $f_c = 664 \text{ Hz}, \varepsilon = 0.0095,$<br>$P_M = 45^\circ$ |

| SRF-PLL | $K_{\rm p} = 1.07, K_{\rm i} = 11.89$                                   | $f_{\rm c} = 46.1 \; {\rm Hz}, P_{\rm M} = 86^{\circ}$            |

| MAF-PLL | $K_{\rm p} = 0.27, K_{\rm i} = 9.3, T_{\omega} = 0.01 \text{ s}$        | $f_{\rm c} = 13.9 \; {\rm Hz}, P_{\rm M} = 43^{\circ}$            |

从表2可以看出,SRF-PLL因为没有外加滤波器,必须降低控制环路频带宽度以滤除电网中的畸波及不平衡分量;MAF-PLL采用环路内加滤波器,不仅减小了频带宽度,而且降低了相角裕度;而本文所提SPLL采用滤波器前置的方式,不仅可以简化锁相环控制环路参数设计,增大带宽,而且增加了系统稳定性。

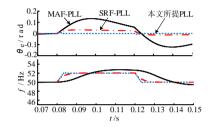

案例1设定的电网情况下,3种锁相环的相位误差及频率响应曲线见附录中图A2。由图可知,MAF-PLL的动态响应速度最慢,为2个电网工频周期,最大相位误差为0.15 rad;SRF-PLL的响应速度为10 ms,最大相位误差为0.06 rad;本文所提SPLL的响应速度仅为3 ms,能够无误差地锁定相位。对比频率响应曲线也可以看出本文所提SPLL具有快速的频率响应。

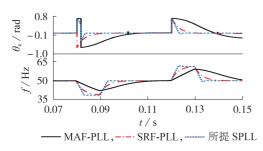

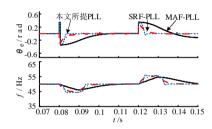

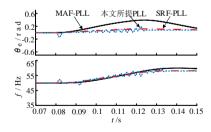

案例2设定的电网情况下,3种锁相环的相位误差 $\theta$ 。及频率f响应曲线如图7所示。由图可知,三者最大相位误差都为0.65 rad,而本文所提SPLL具有最快的响应速度,仅为4 ms。三者都具有较大的频率误差,这是由于传统SPLL的结构相位和频率之间

图7 案例2的相位误差及频率响应

Fig.7 Phase error and frequency response of Case 2 存在较强的耦合关系。

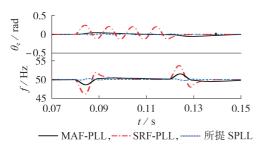

案例3设定的电网情况下,3种锁相环的相位误差及频率响应曲线见图8。由图可知,SRF-PLL在电网发生单相接地故障时,会产生一个幅值为0.2 rad、频率为100 Hz的振荡误差,这是因为通过降低带宽,SRF-PLL仍无法消除电网发生单相接地故障时不平衡电压产生的负序分量;MAF-PLL可以完全滤除单相接地故障时产生的负序分量,但存在相移产生的锁相误差;而本文所提SPLL通过DIF模块消除负序分量,相位误差比MAF-PLL小,且响应速度更快。

图 8 案例 3 的相位误差及频率响应

Fig.8 Phase error and frequency response of Case 3

案例4设定的电网情况下,3种锁相环的相位误差及频率响应曲线见附录中图A3。三者最大相位误差都为0.38 rad,SRF-PLL的响应时间为10 ms,MAF-PLL的响应时间超过1个工频周期,而本文所提SPLL的响应时间仅为4 ms。

案例5设定的电网情况下,3种锁相环的相位误差及频率响应曲线见附录中图A4。当频率发生较大偏移时,本文所提SPLL相较于SRF-PLL及MAF-PLL具有较大的相位误差,且出现振荡。这是由于本文所设计的DIF模块中参考频率是固定值,为额定电网频率。由式(7)可知,当ω与ω"偏差较大时,式(7)的结果也将具有较大的偏差。同样,设计MAF时其参考频率也是固定值,当电网频率发生偏移时,电网中谐波的基波频率也发生偏移,而MAF设计参数不变,其抑制谐波的能力将下降。

为了比较说明本文所提SPLL的优势,将其在上述 仿真案例下的动态响应时间、最大相位误差、最大频率 误差分别与SRF-PLL、MAF-PLL进行了对比分析,结 果如表3所示。可以看出,当电网频率发生±2 Hz以内 偏移时,本文所提SPLL相比SRF-PLL和MAF-PLL 具有更小的相位误差和更快的动态响应速度。

#### 表3 案例仿真结果对比

Table 3 Comparison of case simulative results

|         |    | 1        |       |         |       |

|---------|----|----------|-------|---------|-------|

| 锁相环     | 案例 | 相位最大     | 相位响应  | 频率超     | 频率响应  |

| 坝相小     |    | 误差 / rad | 时间/ms | 调量 / Hz | 时间/ms |

|         | 1  | 0.01     | <3    | 0.2     | <4    |

|         | 2  | 0.65     | <4    | 11      | < 13  |

| 所提SPLL  | 3  | 0.02     | < 8   | 0.3     | < 10  |

|         | 4  | 0.38     | <4    | 6       | <13   |

|         | 5  | 0.10     | _     | 3       | _     |

|         | 1  | 0.06     | <9    | 0.2     | <9    |

|         | 2  | 0.65     | <11   | 10      | < 20  |

| SRF-PLL | 3  | 0.28     | _     | 4       | < 20  |

|         | 4  | 0.38     | < 10  | 6       | < 16  |

|         | 5  | 0.10     | < 10  | 0.1     | < 10  |

|         | 1  | 0.15     | <40   | 0.8     | <40   |

|         | 2  | 0.65     | < 25  | 7       | < 30  |

| MAF-PLL | 3  | 0.04     | < 20  | 2       | < 20  |

|         | 4  | 0.38     | <23   | 4       | < 30  |

|         | 5  | 0.35     | < 40  | 2       | < 20  |

# 4 实验验证

为了进一步验证本文所提SPLL的快速动态响应能力,本文使用TI公司型号为TMS320F28335的数字信号处理器进行实验验证。所有实验都是在电网额定电压为120 V、额定频率为50 Hz的工况下进行的。

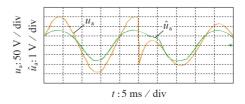

图 9 为当电网发生  $-40^{\circ}$  相位跳变时,所提 SPLL 锁定电网相位时所输出的电压波形。图中, $u_a$  为电网 a 相电压; $\hat{u}_a$  为所提 SPLL输出电压。可以看出,所提 SPLL经过 7 ms 即可重新锁定电网相位。

图 9 电网相位突变时所提 SPLL 的动态响应过程 Fig. 9 Dynamic response of proposed SPLL with sudden change of grid phase

图 10 为当电网发生单相接地故障时,所提 SPLL 锁定电网相位时所输出的电压同电网 b、c 相电压  $u_b$ 、 $u_c$ 的波形。可以看出,所提 SPLL 经过 5 ms 即可

图 10 电网发生单相接地故障时所提 SPLL 的 动态响应过程

Fig.10 Dynamic response of proposed SPLL with single-phase grounding fault

重新锁定电网相位。

附录中图 A5 为当电网中含有 5% 的-5次和 3% 的 7次谐波时,所提 SPLL锁定电网相位时所输出的电压波形。可以看出,所提 SPLL 经过 10 ms 即可重新锁定电网相位。

# 5 结论

针对传统 SPLL 无法抑制电网中不平衡分量以及环内滤波器 SPLL 动态响应时间慢的问题,本文基于 MAF 进行滤波器前置 SPLL 的设计。与环路内滤波器结构相比,采用环路外前置滤波器结构可将开环环路带宽提高 47倍,相角裕度增加 2°。另外通过 DIF 模块将 MAF 的响应时间由 0.01 s减小至 0.003 3 s。与 MAF-SPLL 相比,通过对 MAF 进行线性相移补偿,消除了锁相误差。需要注意的是,本文所提 SPLL 对电网频率发生较大偏移的适应性不强,仅考虑了电网频率发生 ±2 Hz 偏移的情况,接下来将针对所提 SPLL 进行频率自适应方面的研究。

附录见本刊网络版(http://www.epae.cn)。

# 参考文献:

- [1] 熊连松,卓放,刘小康,等. 不对称电网同步相位的快速开环捕获方法研究[J]. 中国电机工程学报,2015,35(22):5682-5691. XIONG Liansong, ZHUO Fang, LIU Xiaokang, et al. Research on fast open-loop acquisition method of synchronous phase in asymmetric power grid[J]. Proceedings of the CSEE,2015,35 (22):5682-5691.

- [2] 马茜,汪玉婷. 基于 QT1 结构的三相增强型锁相环技术[J]. 电力自动化设备,2020,40(9):35-41.

MA Qian, WANG Yuting. Three phase enhanced phase locked loop technology based on QT1 structure[J]. Electric Power Automation Equipment,2020,40(9):35-41.

- [3] 杜雄,郭宏达,孙鹏菊,等. 基于 ANF-PLL 的电网电压基波正 负序分离方法[J]. 中国电机工程学报,2013,33(27):28-35,6. DU Xiong,GUO Hongda,SUN Pengju, et al. The method of separating the positive and negative sequence of fundamental voltage based on ANF-PLL[J]. Proceedings of the CSEE,2013, 33(27):28-35,6.

- [4] EREN S, KARIMI-GHARTEMANI M, BAKHSHAI A. Enhancing the three-phase synchronous reference frame PLL to remove unbalance and harmonic errors [C]//2009 35th Annual Conference of IEEE Industrial Electronics. Porto, Portugal: IEEE, 2009:437-441.

- [5] GUO X, WU W, CHEN Z. Multiple-complex coefficient-filter-based phase-locked loop and synchronization technique for three-phase grid-interfaced converters in distributed utility networks [J]. IEEE Transactions on Industrial Electronics, 2011, 58(4):1194-1204.

- [6] 王佳浩,潘欢,纳春宁. 电网电压不平衡和谐波畸变下新型 并网锁相环设计[J]. 电力系统保护与控制,2019,47(15): 108-115.

- WANG Jiahao, PAN Huan, NA Chunning. Design of a new type of grid connected PLL under unbalanced and distorted voltage[J]. Power System Protection and Control, 2019, 47(15): 108-115.

- [7] WANG Y F, LI Y W. Grid synchronization PLL based on cascaded delayed signal cancellation[J]. IEEE Transactions on

- Power Electronics, 2011, 26(7): 1987-1997.

- [8] 吉正华,韦芬卿,杨海英. 基于 dq 变换的三相软件锁相环设计 [J]. 电力自动化设备,2011,31(4):104-107.

JI Zhenghua, WEI Fenqing, YANG Haiying. Design of three-phase software PLL based on dq transformation[J]. Electric Power Automation Equipment,2011,31(4):104-107.

- [9] GOLESTAN S,FREIJEDO F D,VIDAL A,et al. A quasi-type-1 phase-locked loop structure[J]. IEEE Transactions on Power Electronics, 2014, 29(12):6264-6270.

- [10] WANG J, LIANG J, GAO F, et al. A method to improve the dynamic performance of moving average filter-based PLL[J]. IEEE Transactions on Power Electronics, 2015, 30(10):5978-5990

- [11] ROBLES E, CEBALLOS S, POU J, et al. Variable-frequency grid-sequence detector based on a quasi-ideal low-pass filter stage and a phase-locked loop[J]. IEEE Transactions on Power Electronics, 2010, 25(10):2552-2563.

- [12] GOLESTAN S, GUERRERO J M, VASQUEZ J C. Three-phase PLLs; a review of recent advances [J]. IEEE Transactions on Power Electronics, 2017, 32(3):1894-1907.

- [13] GOLESTAN S, MONFARED M, FREIJEDO F D. Design-oriented study of advanced synchronous reference frame phase-locked loops[J]. IEEE Transactions on Power Electronics, 2013,28(2):765-778.

- [14] GOLESTAN S,RAMEZANI M,GUERRERO J M, et al. Moving average filter based phase-locked loops; performance analysis and design guidelines [J]. IEEE Transactions on Power Electronics, 2014, 29(6):2750-2763.

- [15] 张国庆,王贵忠,吴志琪,等. 一种改进型两相静止坐标系增强型锁相环[J]. 电力自动化设备,2018,38(8):59-67. ZHANG Guoqing, WANG Guizhong, WU Zhiqi, et al. An improved enhanced phase locked loop in two phase stationary coordinate system[J]. Electric Power Automation Equipment, 2018,38(8):59-67.

- [16] GOLESTAN S, GUERRERO J M, ABUSORRAH A M. MAF-PLL with phase-lead compensator[J]. IEEE Transactions on Industrial Electronics, 2015, 62(6); 3691-3695.

- [17] FREIJEDO F D, DOVAL-GANDOY J, LÓPEZ Ó, et al. Tuning of phase-locked loops for power converters under distorted utility conditions [J]. IEEE Transactions on Industry Applications, 2009, 45(6):2039-2047.

- [18] FREIJEDO F D, DOVAL-GANDOY J, LÓPEZ Ó, et al. A generic open-loop algorithm for three-phase grid voltage / current synchronization with particular reference to phase, frequency, and amplitude estimation[J]. IEEE Transactions on Power Electronics, 2009, 24(1):94-107.

- [19] MIRHOSSEINI M, POU J, AGELIDIS V G, et al. A three-phase frequency-adaptive phase-locked loop for independent single-phase operation [J]. IEEE Transactions on Power Electronics, 2014, 29(12):6255-6259.

#### 作者简介:

刘启德

刘启德(1994—),男,新疆乌鲁木齐人,硕士研究生,主要研究方向为可再生能源发电与并网技术(E-mail: 1033362410@qq.com);

王海云(1973—),女,新疆乌鲁木齐人,教授,博士研究生导师,主要研究方向为可再生能源发电与并网技术(E-mail: 327028229@qq.com)。

(编辑 李莉)

(下转第151页 continued on page 151)

# DWT-PNN based fault detection method for flexible DC transmission system

JIN Tao<sup>1,2</sup>, ZHANG Ke<sup>1</sup>, CHEN Jian<sup>1</sup>

- (1. College of Electrical Engineering and Automation, Fuzhou University, Fuzhou 350116, China;

- 2. Fujian Key Laboratory of New Energy Generation and Power Conversion, Fuzhou 350108, China)

Abstract: The failure of the flexible DC transmission system greatly affects the stability of power system. The existing transmission line fault detection methods have the problems of difficult threshold selection, sensitivity to transition resistance changes and long detection time. A method of fault type detection and position discrimination based on wavelet energy ratio using PNN(Probabilistic Neural Network) is proposed. The frequency characteristics of the transient voltage are obtained by fast Fourier analysis of the measured voltages of the bus and line under different fault types, and then DWT(Discrete Wavelet Transform) is used to obtain the wavelet energy characteristics at different scales. The fault type and fault location can be determined accurately according to the output results of PNN. The electromagnetic transient model of the four-terminal flexible DC transmission network is built under PSCAD / EMTDC environment. The simulative results show that the proposed method can detect the fault type and fault location of high resistance grounding fault accurately, without being affected by the transition resistance.

**Key words:** flexible DC transmission system; fault detection; wavelet transform; wavelet energy ratio; probabilistic neural network

\_\_\_\_\_

(上接第129页 continued from page 129)

# Design of three-phase software phase locked loop based on prefilter

LIU Qide<sup>1</sup>, WANG Haiyun<sup>1</sup>, WANG Haocheng<sup>2</sup>, XU Yong<sup>1</sup>

- (1. Research Center of Renewable Energy Generation and Grid-connected Control Engineering Technology, Ministry of Education, College of Electrical Engineering, Xinjiang University, Urumqi 830047, China;

- 2. College of Electronic and Information Engineering, Yili Normal University, Yining 835000, China)

Abstract: In order to solve the problems of large phase-locked error and slow dynamic response of traditional SPLL(Software Phase Locked Loop) under unbalanced and distorted voltage, a prefilter SPLL based on MAF(Moving Average Filter) is proposed, which is based on the principle of traditional SPLL. A fast unbalanced component suppression and phase delay compensation method is applied to improve the performance of MAF, which effectively improves the dynamic response speed and phase-locked accuracy of the proposed SPLL. Through MATLAB/Simulink simulation platform and TMS320F28335 DSP(Digital Signal Processor) chip, the control strategy of the proposed SPLL is verified under the condition of three-phase voltage unbalance and voltage distortion. The results show that the SPLL has small phase-locked error, fast dynamic response speed and high stability.

**Key words:** software phase locked loop; moving average filter; phase delay compensation; voltage distortion; digital signal processor

# 附录

图 A1 传统 SPLL 的结构框图.

Fig.A1 Schematic diagram of conventional SPLL

图 A2 案例 1 的相位误差及频率响应

Fig.A2 Phase error and frequency response of Case 1

图 A3 案例 4 的相位误差及频率响应

Fig.A3 Phase error and frequency response of Case 4

图 A4 案例 5 的相位误差及频率响应

Fig.A4 Phase error and frequency response of Case 5

图 A5 电网含有谐波时锁相环的动态响应过程.

Fig.A5 Dynamic response of PLL with grid harmonic